# Real-Time Multitasking in Embedded Systems Based on Reconfigurable Hardware

Dissertation

A thesis submitted to the Faculty of Computer Science, Electrical Engineering and Mathematics of the University of Paderborn in partial fulfillment of the requirements for the degree of Dr. rer. nat.

by

## Klaus Danne

Paderborn, Germany date of submission: 11.9.2006

Supervisors: Prof. Dr. Franz J. Rammig Prof. Dr. Marco Platzner

Reviewers:

Prof. Dr. Franz J. Rammig Prof. Dr. Marco Platzner Prof. Dr. Daniel D. Gajski

$\label{eq:additional members of the oral examination committee:$

Prof. Dr. Ulrich Rückert Dr. Ulf Lorenz

Date of submission: September 11, 2006

September 11, 2000

Date of public examination: November 22, 2006

# Acknowledgements

This PhD thesis was carried out during my work at the University of Paderborn in Germany as a member of the *Design of Parallel Systems* group under Prof. Dr. Franz. J. Rammig, from July 2002 to June 2005, and as a member of the *Computer Engineering* group under Prof. Dr. Marco Platzner, from July 2005 to November 2006. The work was partially supported by the German Research Foundation (Deutsche Forschungsgemeinschaft) in the research training group 776 Automatic Configuration in Open Systems.

I would like to thank Prof. Rammig for supervising my thesis, supporting my work as member of his group, and sharing in his great knowledge concerning embedded systems and computer science research in general. Likewise, I thank my co-supervisor Prof. Platzner. He employed me as a researcher just shortly after he became professor at Paderborn University and supported a great part of my publications as co-author. In addition, my thanks go to Prof. Dr. Daniel D. Gajski, who was a third reviewer as well as Prof. Dr. Ulrich Rückert and Dr. Ulf Lorenz, who were additional members of the oral examination commission.

Further, without mentioning everyone personally, I would like to thank many colleagues that helped me during my time at Paderborn University:

Prof. Dr. Christophe Bobda as a coauthor of several publications and for proofreading my thesis; my teammates Dr. Stefan Ihmor and Florian Dittmann for constructive and interesting discussions; Tales Heimfahrt and Marcelo Götz for teaching me the Brazilian thinking and fixing my Linux PC; my new teammates Paul Kaufmann, Enno Lübbers and Heiner Giefers for all the discussions. I am also grateful to Tarek Zeineldin and our working group visitors Prof. Dr. David Andrews and Jason Agron for proofreading the thesis. Further acknowledgments go to Dr. Heiko Kalte for co-authoring publications and to Roland Mühlenbernd and Martin Kreis for supporting my research as student assistants and by their bachelor's and master's theses respectively.

Finally, I would like to thank my parents for their great support during my education, my sister for being a good friend, and my lovely girlfriend Sonja for stepping into my life.

Klaus Danne, December 2006

# Contents

| Lis | List of Figures                   |                                                                                                                                            |                                   |  |  |  |

|-----|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|

| Lis | st of                             | Tables                                                                                                                                     | ix                                |  |  |  |

| Ab  | ostrac                            | t                                                                                                                                          | 1                                 |  |  |  |

| 1   | <b>Intro</b><br>1.1<br>1.2<br>1.3 | Oduction         Motivation to Real-Time Multitasking         Contribution of This Thesis         Chapter Outline                          | <b>3</b><br>4<br>6<br>7           |  |  |  |

| 2   | <b>Bac</b><br>2.1                 | kground and Related Work         Reconfigurable Hardware Devices                                                                           | <b>9</b><br>10                    |  |  |  |

|     |                                   | 2.1.1Fine-Grain RHDs (FPGAs)2.1.2Coarse-Grain RHDs                                                                                         | $10 \\ 12$                        |  |  |  |

|     |                                   | 2.1.3 Configuration Memory and Reconfiguration                                                                                             | $12 \\ 13 \\ 14$                  |  |  |  |

|     | 2.2                               | 2.1.4       Architecture of RHD Based Computer Platforms         Hardware Tasks                                                            | 16                                |  |  |  |

|     | 2.3                               | Multi-Tasking on Reconfigurable Hardware2.3.1Resource Sharing Models2.3.2Task Scheduling and Placement Methods for RHDs                    | 20<br>20<br>26                    |  |  |  |

|     | 2.4                               | <ul> <li>2.3.3 Dynamic Reconfigurable Systems</li></ul>                                                                                    | 26<br>30<br>30<br>31<br>33<br>38  |  |  |  |

|     | 2.5                               | Chapter Conclusion                                                                                                                         | 38<br>40                          |  |  |  |

| 3   | Prot<br>3.1<br>3.2<br>3.3<br>3.4  | Dem Modeling and Metrics         Task and Resource Models         Feasible Schedule         Utilization Metrics         Chapter Conclusion | <b>43</b><br>43<br>47<br>48<br>50 |  |  |  |

| 4 | Thr | ee Scho | eduling Algorithms                                |

|---|-----|---------|---------------------------------------------------|

|   | 4.1 |         | l Scheduling                                      |

|   |     | 4.1.1   | Earliest Deadline First on RHDs                   |

|   |     | 4.1.2   | Relation to Multiprocessor EDF                    |

|   |     | 4.1.3   | Schedulability Analysis for EDF-FkF               |

|   |     | 4.1.4   | Conclusion on global EDF                          |

|   | 4.2 | Partit  | ioned Scheduling                                  |

|   |     | 4.2.1   | Partitioned Scheduling on RHDs                    |

|   |     | 4.2.2   | Relation to 2-Dimensional Packing Problems        |

|   |     | 4.2.3   | Optimal Partitioning by ILP                       |

|   |     | 4.2.4   | Next-Fit-Decreasing-Area Partitioning             |

|   |     | 4.2.5   | Conclusion on Partitioned EDF                     |

|   | 4.3 | Server  | r-Based Scheduling                                |

|   |     | 4.3.1   | The Merge-Server Distribute Load (MSDL) Algorithm |

|   |     | 4.3.2   | Exact Evaluation of Computation Time Reduction    |

|   |     | 4.3.3   | Properties of MSDL                                |

|   |     | 4.3.4   | Conclusion on Server-Based Scheduling             |

|   | 4.4 | Chapt   | er Conclusion                                     |

| 5 | Con | npariso | n of Algorithm Scheduling Performance             |

|   | 5.1 | -       | tical Comparison and Scheduling Anomalies         |

|   | 5.2 |         | ation Results                                     |

|   |     | 5.2.1   | Creation of Benchmarks                            |

|   |     | 5.2.2   | Performance on Standard Benchmark $BM_{std}$      |

|   |     | 5.2.3   | Impact of Area and Time-utilization               |

|   |     | 5.2.4   | Performance of Combined Algorithms                |

|   |     | 5.2.5   | Impact of Number of Tasks                         |

|   | 5.3 | Concl   | usion on Algorithm Performance                    |

| 6 | Exe | cution  | Model and Overhead Analysis                       |

| Č | 6.1 |         | l EDF Overhead Model                              |

|   | 0.1 | 6.1.1   | Reconfiguration Modes and Task Placement          |

|   |     | 6.1.2   | Runtime System Requirements                       |

|   |     | 6.1.3   | Reconfiguration Overheads                         |

|   | 6.2 |         | ioned EDF Overhead Model                          |

|   |     | 6.2.1   | Reconfiguration Modes and Task Placement          |

|   |     | 6.2.2   | Runtime System Requirements                       |

|   |     | 6.2.3   | Reconfiguration Overheads                         |

|   | 6.3 |         | Based MSDL Overhead Model                         |

|   |     | 6.3.1   | Reconfiguration Modes and Task Placement          |

|   |     | 6.3.2   | Runtime System Requirements                       |

|   |     | 6.3.3   | Reconfiguration Overheads                         |

|   | 6.4 |         | rmance Evaluation Including Overhead              |

|   |     | 6.4.1   | Global EDF Overhead Evaluation                    |

|   |     | 6.4.2   | Partitioned EDF Overhead Evaluation               |

|   |     | 6.4.3   | Server Based MSDL Overhead Evaluation             |

|                    | 6.5            | Conclusion on Execution Models and Overhead                             |              |  |  |  |

|--------------------|----------------|-------------------------------------------------------------------------|--------------|--|--|--|

| 7 Model Extensions |                |                                                                         |              |  |  |  |

|                    | 7.1            | Periodic Tasks with Variants                                            | 115          |  |  |  |

|                    |                | 7.1.1 Variant-Rich Tasks                                                | 116          |  |  |  |

|                    |                | 7.1.2 Partitioned Scheduling of Variant-Rich Tasks                      | 119          |  |  |  |

|                    |                | 7.1.3 Optimal Partitioning by ILP                                       | 121          |  |  |  |

|                    |                | 7.1.4 Performance Evaluation for Variant-Rich Tasks                     | 124          |  |  |  |

|                    |                | 7.1.5 Approaches for Global- and Server Scheduling of Variant-Rich Task | <b>s</b> 126 |  |  |  |

|                    | 7.2            | Periodic Tasks with Memory Access                                       | 128          |  |  |  |

|                    |                | 7.2.1 The Buffer Assignment Problem                                     | 129          |  |  |  |

|                    |                | 7.2.2 Task Schedule Aware Buffer Assignment                             | 132          |  |  |  |

|                    |                | 7.2.3 Buffer Assignment Based on Integer Programming                    | 134          |  |  |  |

|                    |                | 7.2.4 Simulation Results                                                | 135          |  |  |  |

|                    |                | 7.2.5 Concluding Discussion on Memory Demanding RT Applications         | 136          |  |  |  |

|                    | 7.3            | Chapter Conclusion                                                      | 137          |  |  |  |

| 8                  | Prot           | otype: FPGA Based Real-Time Kernel                                      | 139          |  |  |  |

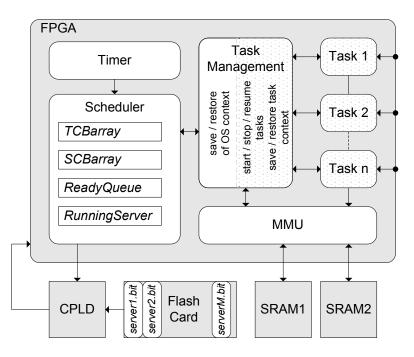

|                    | 8.1            | System Architecture                                                     | 139          |  |  |  |

|                    |                | 8.1.1 An All-Hardware Runtime System                                    | 139          |  |  |  |

|                    |                | 8.1.2 Scheduler Data Structures                                         | 141          |  |  |  |

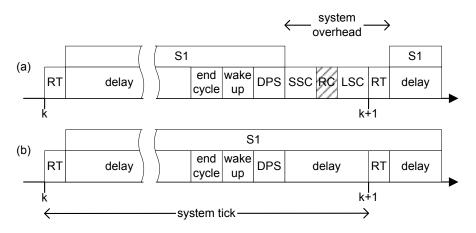

|                    |                | 8.1.3 The Scheduler Cycle                                               | 142          |  |  |  |

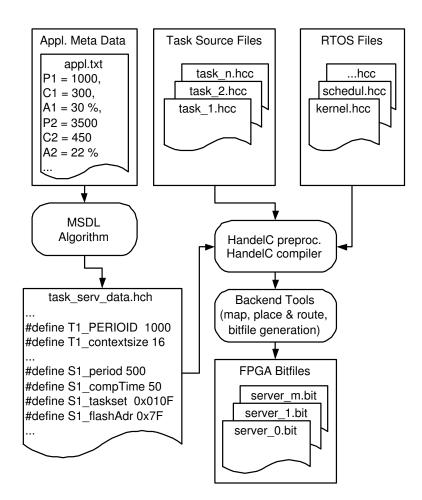

|                    | 8.2            | Synthesis Tool Flow                                                     | 143          |  |  |  |

|                    | 8.3            | Synthesis Results                                                       | 145          |  |  |  |

|                    | 8.4            | Chapter Conclusion                                                      | 146          |  |  |  |

| 9                  | Con            | clusion and Outlook                                                     | 149          |  |  |  |

|                    | 9.1            | Summary                                                                 | 149          |  |  |  |

|                    | 9.2            | Drawn Conclusions                                                       | 150          |  |  |  |

|                    | 9.3            | Outlook and Future Work                                                 | 152          |  |  |  |

| Au                 | thor'          | s Publications                                                          | 155          |  |  |  |

| Bil                | Bibliography 1 |                                                                         |              |  |  |  |

Contents

# List of Figures

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Basic structure of an FPGAStructure of FPGA logic blockArchitecture of an RHD based platformExample of a DCT task on platformResource sharing approaches based on full configurationRHD Resource sharing approaches based on partial RHD configuration. | $11 \\ 11 \\ 15 \\ 16 \\ 21 \\ 23$ |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

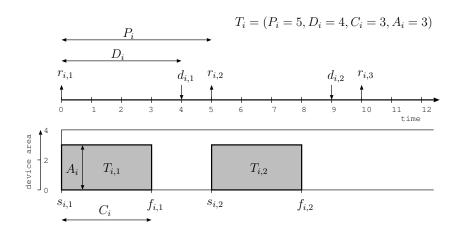

| 3.1<br>3.2                             | Parameters of a single aperiodic job                                                                                                                                                                                                                    | 44<br>44<br>46                     |

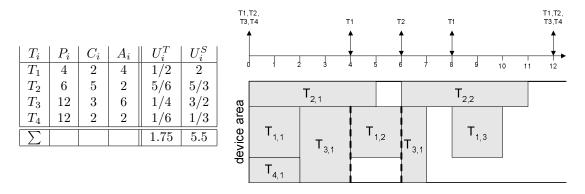

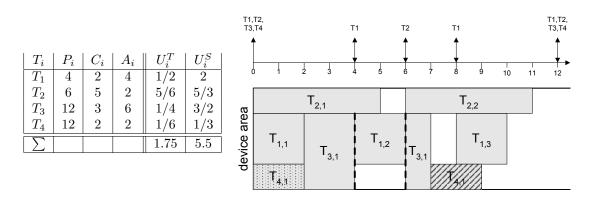

| 3.3<br>3.4<br>3.5                      | Parameters of a periodic task $\dots$ Example task set $\Gamma^*$ and a feasible schedule. $\dots$ Scheduling Anomaly: An infeasible task set with infinitesimal system                                                                                 | 40<br>48                           |

|                                        | utilization                                                                                                                                                                                                                                             | 50                                 |

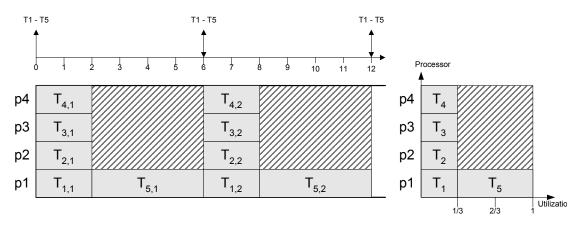

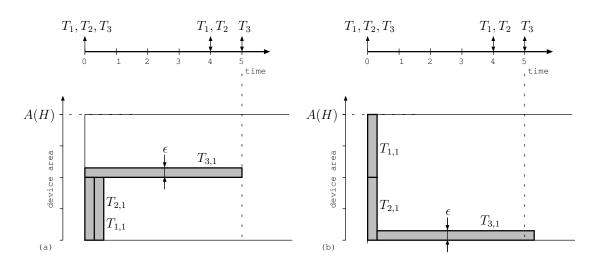

| 4.1                                    | A schedule for $\Gamma^*$ by $EDF$ - $FkF$ vs. $EDF$ - $NF$                                                                                                                                                                                             | 55                                 |

| 4.2                                    | EDF multiprocessor schedule                                                                                                                                                                                                                             | 56                                 |

| 4.3                                    | $EDF$ - $FkF$ schedule of $\hat{\Gamma}$                                                                                                                                                                                                                | 61                                 |

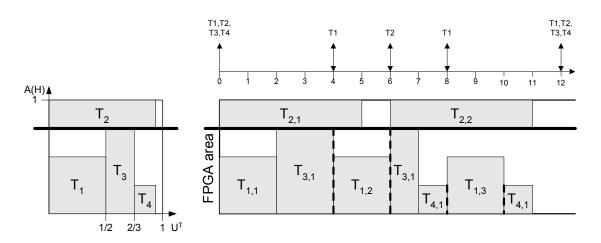

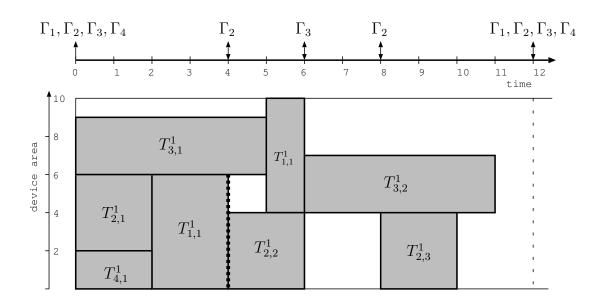

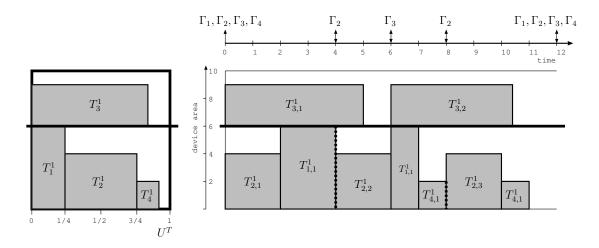

| 4.4                                    | Example partitioning of $\Gamma^*$ and the according schedule                                                                                                                                                                                           | 65                                 |

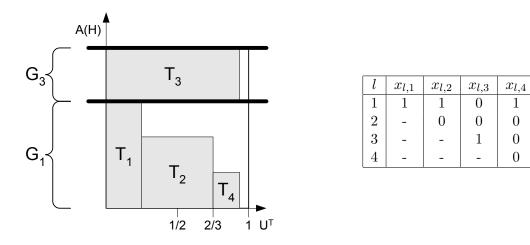

| 4.5                                    | Example of partitioning $\chi$ and the according decision variable configuration                                                                                                                                                                        | 69                                 |

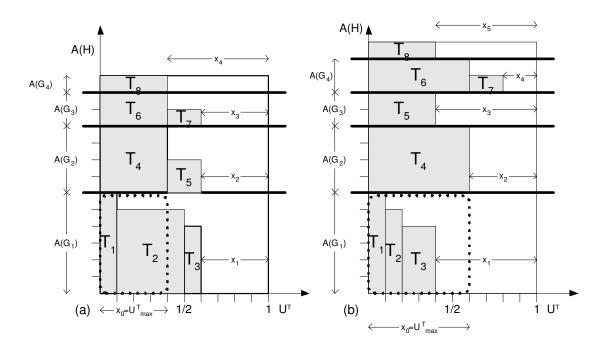

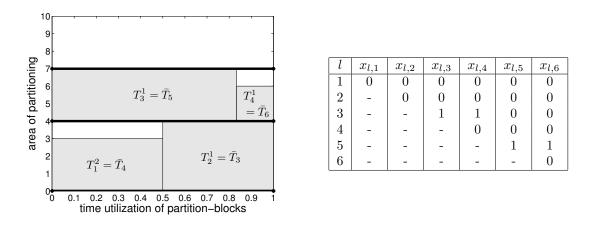

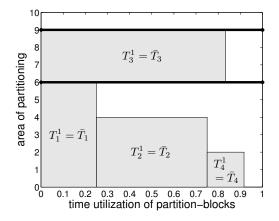

| 4.6                                    | Example partitioning of NFDA for (a) a task set with $U_{max}^T \leq 0.5$ and                                                                                                                                                                           |                                    |

|                                        | (b) a task set with $U_{max}^T > 0.5$                                                                                                                                                                                                                   | 71                                 |

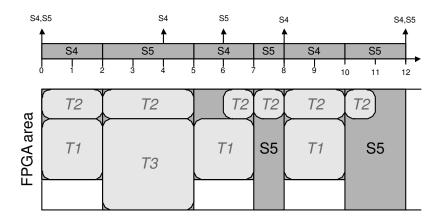

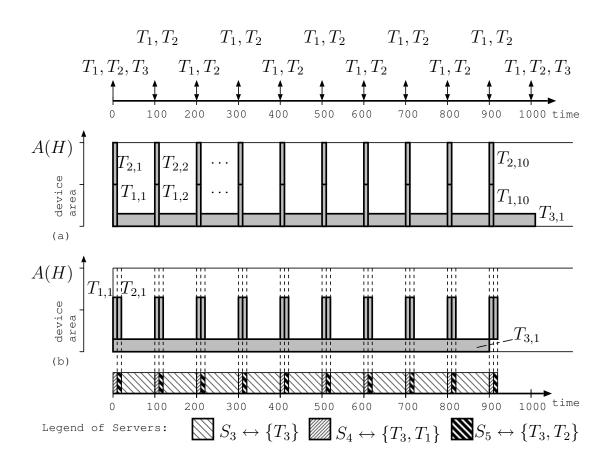

| 4.7                                    | Schedule of server task set generated by MSDL                                                                                                                                                                                                           | 78                                 |

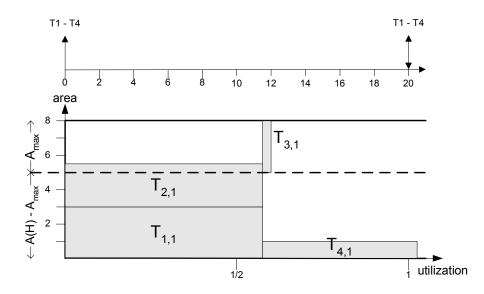

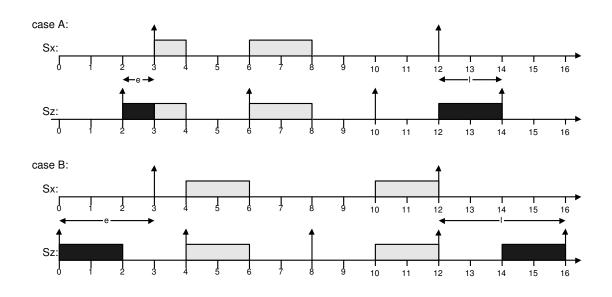

| 4.8                                    | Case analysis of computation time reduction                                                                                                                                                                                                             | 79                                 |

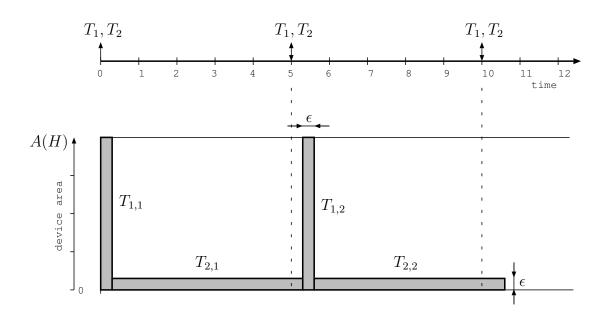

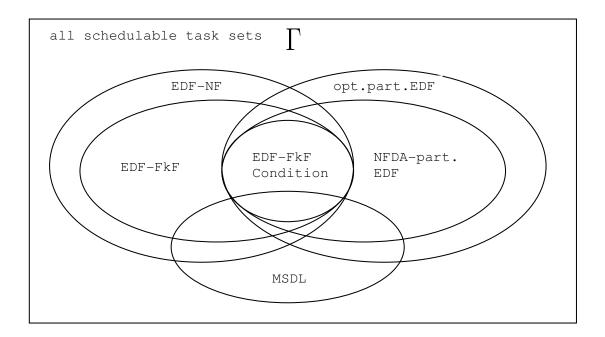

| 5.1                                    | Scheduling anomaly: A task set infeasible by <i>any</i> partitioned schedule, but feasibly by global <i>EDF-NF</i> .                                                                                                                                    | 84                                 |

| 5.2                                    | Scheduling anomaly: A task set infeasible by global $EDF-NF$ but feasible                                                                                                                                                                               |                                    |

|                                        | by partitioned EDF <i>NFDH</i>                                                                                                                                                                                                                          | 85                                 |

| 5.3                                    | Scheduling anomaly: A task set infeasible by global $EDF-NF$ but feasible                                                                                                                                                                               |                                    |

|                                        | by <i>MSDL</i>                                                                                                                                                                                                                                          | 88                                 |

| 5.4                                    | The relation between feasibly scheduled task sets by the proposed algo-<br>rithms as VENN-diagram.                                                                                                                                                      | 89                                 |

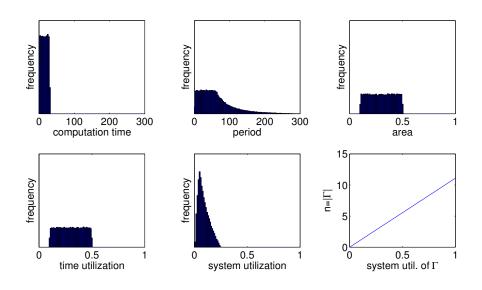

| 5.5                                    | Characteristics of $BM_{sdt}$ tasks and task sets                                                                                                                                                                                                       | 92                                 |

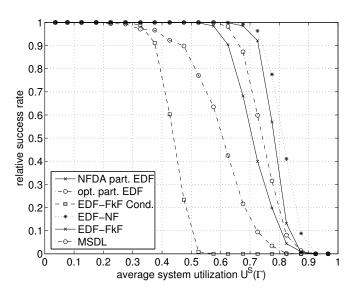

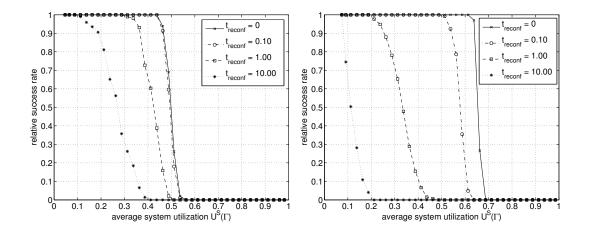

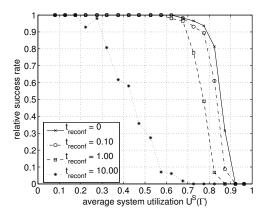

| 5.6                                    | Performance of algorithms on $BM_{sdt}$                                                                                                                                                                                                                 | 93                                 |

|                                        |                                                                                                                                                                                                                                                         |                                    |

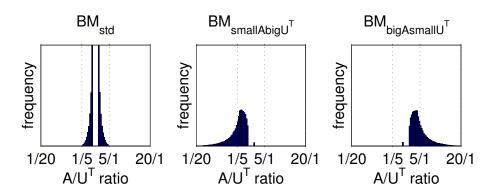

| 5.7          | Distribution of the tasks' $A_i$ to $U^T(T_i)$ ratio of the $BM_{sdt}, BM_{smallAbigU^T}$<br>and $BM_{bigAsmallU^T}$ benchmarks.                       | 94                                        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

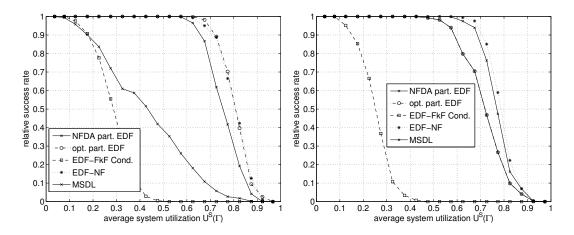

| 5.8          | Performance of algorithms on $BM_{smallAbigU^T}$ and $BM_{bigAsmallU^T}$ benchmarks.                                                                   | 95                                        |

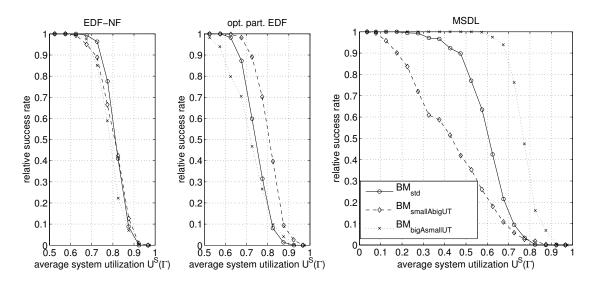

| 5.9          | Performance of algorithms $EDF$ - $NF$ , $opt$ - $part$ - $EDF$ and $MSDL$ on the $BM_{std}$ , $BM_{smallAbigU^T}$ and $BM_{bigAsmallU^T}$ benchmarks. | 96                                        |

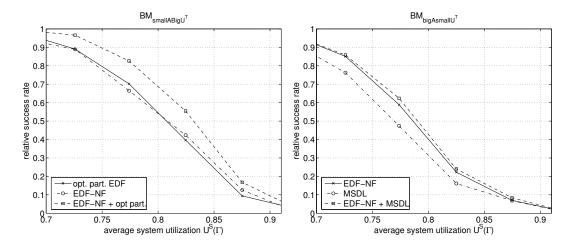

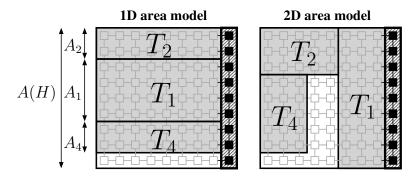

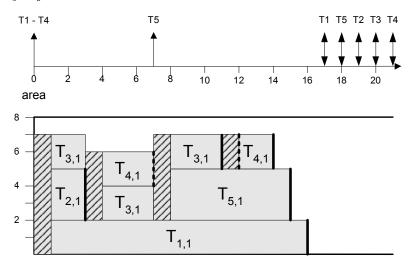

|              | Performance of combined algorithms on $BM_{smallAbigU^T}$ and $BM_{bigAsmallU^T}$ benchmarks.                                                          | 97                                        |

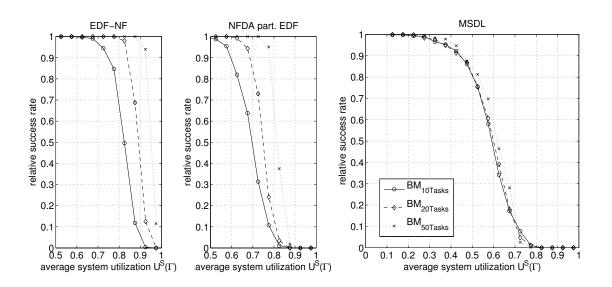

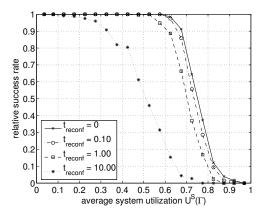

| 5.11         | Performance of algorithms <i>EDF-NF</i> , <i>NFDA-partEDF</i> and <i>MSDL</i> on task sets with 10, 20 and 50 tasks.                                   | 99                                        |

| 6.1<br>6.2   | Partial reconfiguration models supporting arbitrary task areas A schedule including reconfiguration times                                              | $\begin{array}{c} 102 \\ 103 \end{array}$ |

| 6.3<br>6.4   | Performance of the EDF-FkF scheduling test including reconfiguration<br>overhead                                                                       | 111                                       |

| 0.4<br>6.5   | figuration overheads $(BM_{std})$<br>Performance of optpartitioned-EDF including reconfiguration overheads                                             | 111                                       |

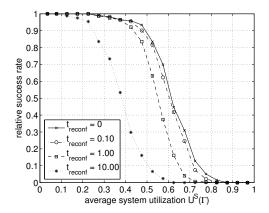

| 6.6          | $(BM_{std})$                                                                                                                                           | 112<br>113                                |

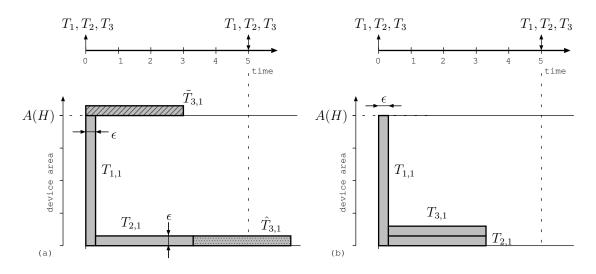

| 7.1          | Preemptive global schedule of variant-rich tasks                                                                                                       | 118                                       |

| 7.2<br>7.3   | Example of a partitioned EDF schedule of a variant-rich task set Optimal partitioning of $F^*$ and the according decision variable configuration       | 120 $124$                                 |

| 7.4          | Sub-optimal partitioning of $F^*$ , considering only the first variant of each task.                                                                   | 124                                       |

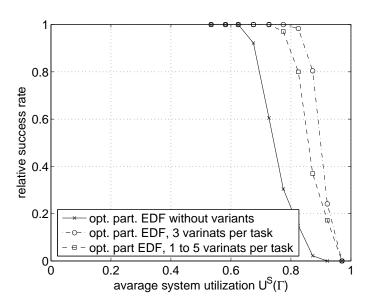

| 7.5<br>7.6   | Application of Example 4 mapped to a reconfigurable platform                                                                                           | 125<br>129                                |

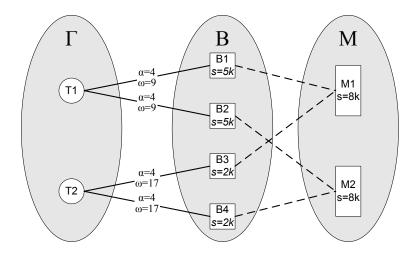

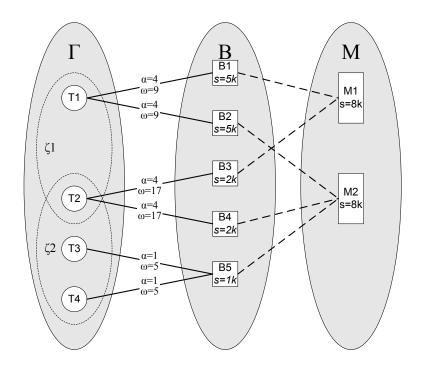

| 7.7<br>7.8   | Graph representation of the memory demanding RT application of Ex-<br>ample 4                                                                          | 131                                       |

| 1.0          | running sets of a task schedule.                                                                                                                       | 134                                       |

| $8.1 \\ 8.2$ | System architecture                                                                                                                                    | $140\\142$                                |

| 8.3          | Synthesis tool flow                                                                                                                                    | 144                                       |

# List of Tables

| 2.1 | Characteristics of a XILINX 8 point 1D-DCT IP core                                           | 17  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison of resource sharing models                                                        | 25  |

| 4.1 | Example task set $\hat{\Gamma}$                                                              | 61  |

| 4.2 | Example task set $\Gamma^*$                                                                  | 64  |

| 4.3 | Servers generated for the example task set $\Gamma^*$ by the $MSDL$ algorithm .              | 78  |

| 5.1 | Example of a task set $\Gamma^A$ without feasible partitioning $\ldots \ldots \ldots \ldots$ | 84  |

| 5.2 | Example task set $\Gamma^B$                                                                  | 85  |

| 5.3 | Example task set $\Gamma^D$ without feasible partitioning and feasible set of                |     |

|     | servers $\Omega^D$                                                                           | 86  |

| 5.4 | Example task set $\Gamma^E$                                                                  | 87  |

| 5.5 | Feasible $MSDL$ servers for task set $\Gamma^E$                                              | 87  |

| 5.6 | Benchmark parameters                                                                         | 94  |

| 7.1 | Example of a variant-rich task set $F^*$                                                     | 116 |

| 7.2 | Example of a <i>variant-rich</i> task set $F^*$                                              | 123 |

| 7.3 | Characteristics of a XILINX 8 point 1D-DCT IP core                                           | 129 |

| 7.4 | Simulation results of 2C-BA and SA-BA problems                                               | 136 |

| 8.1 | Runtime system size for various numbers of tasks and servers                                 | 146 |

List of Tables

## Abstract

This thesis presents fundamental work in the new area of multi-tasking on reconfigurable hardware devices (RHDs) under real-time conditions.

RHDs can now execute several hardware-tasks (computations implemented as digital circuits) in parallel due to the increasing logic capacity, as well as sequentially due to runtime reconfiguration capabilities. To use RHDs for real-time workloads of embedded system applications, scheduling techniques and execution environments that create predictable task timings are required.

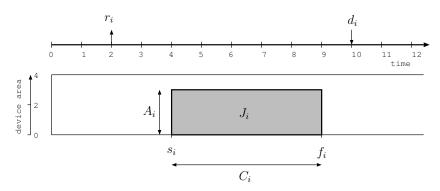

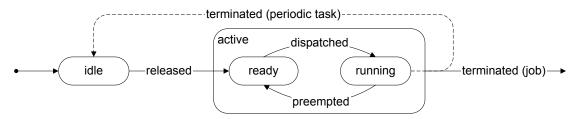

Specifically, we consider the problem of scheduling periodic real-time tasks for execution on shared RHD resources, which makes the problem different from single- and multiprocessor scheduling. In our first model, tasks are modeled by their resource requirements (area), their inter-arrival period and their computation time. Tasks can be executed in parallel as long as their accumulated area does not exceed the device area and can be preempted at any time. We develop three novel *earliest deadline first (EDF)* based scheduling methods and evaluate their performance.

- 1. The global EDF scheduler assigns device resources to all active tasks globally. For this algorithm we present a *linear-time scheduling test* which proves for a given task set at design time that it will be scheduled without missing any deadlines.

- 2. The *partitioned EDF* scheduler divides a task set at design-time into several subsets. Each subset is scheduled independently according to the EDF rule onto separate device resources. The feasibility of the schedule is achieved by considering the single processor EDF bound during partitioning. Integer linear programming (ILP) is used to compute the optimal partitioning while a next fit heuristic computes close to optimal results for even large task sets.

- 3. *MSDL* is a server based scheduling method which groups tasks into periodic servers for parallel execution. At runtime, servers are loaded onto the RHD and executed according to EDF. Only one server is running at a time, making this algorithm suitable for RHDs which do not support partial reconfiguration.

In our analytic performance comparison we show that there is no dominance among the three approaches. However, our simulation studies show that, on average, global EDF outperforms partitioned EDF, which outperforms MSDL. Further we showed that the global EDF scheduling test is rather pessimistic. We analyze the reconfiguration overheads for all three approaches and include them within the schedulability tests. Simulation experiments show that *global EDF* suffers significantly more from this overhead than the other schedulers.

Two extensions of our task model are presented in order to consider the specific characteristics of reconfigurable applications: First we consider tasks for which not only one but several alternative implementations (circuits) exist. We present an ILP model to select the optimal implementations for the partitioned EDF scheduler, which considerably improves the scheduling performance. Second, we consider tasks memory usage under real-time constraints. We present a method for efficiently sharing RAM-banks without jeopardizing task deadlines, thus reducing the required memory resources.

Finally we describe our prototype FPGA based real-time kernel which, in contrast to others, is a hardware-only system with the operating system functions entirely implemented in hardware. Our prototype implements MSDL, uses full device reconfiguration, and is thus suitable for most of today's reconfigurable devices.

In summary, the thesis presents a foundation for real-time multitasking on RHDs, including models, algorithms, analysis and prototypical implementation.

# CHAPTER 1

## Introduction

The aim of this thesis is to enable the use of runtime reconfigurable hardware for computing time-critical tasks in embedded systems.

Besides circuit prototyping and glue-logic replacement there are two major application domains where reconfigurable hardware devices (RHDs) are most useful: *High Performance Computing* and *Embedded Systems*.

In high performance computing, RHDs can be used to speed up special applications. Example systems which have achieved enormous speedups by using pure *field programmable gate array* (FPGA) solutions or FPGAs as co-processors of host computers can be found in [31][95]. Cray's XD1 machine [34] is a commercial example for super-computing using XILINX FPGAs. Also not the application domain targeted by this work, several of the methods explored within this thesis may be equally applicable within high performance computing systems.

In the application domain of embedded systems, RHD based platforms are gaining in popularity and are sometimes preferred to microprocessor based systems because they can:

- respond to input values within very short latencies (shorter than software solutions),

- achieve high throughputs in data flow driven applications (parallelism within a task),

- process many computations in parallel without decrease in performance (multitasking in space),

- communicate to peripheral devices via high number of user definable I/O pins.

Applications within the embedded systems domain include *network-* and *communications systems* such as Ethernet switches, *data processing applications* and *industrial measurement systems* like digital logic analyzers, *military and aerospace systems* as for example satellites, *digital imaging and video systems* such as digital cameras, *consumer electronics* such as audio players, *automotive applications* such as Siemens car entertainment system VDO Dayton and many more [45][55][4].

The applications mentioned above share some common key characteristics:

- they contain computations which are mostly regular, data flow oriented and include digital signal processing, which can be efficiently computed on RHDs,

- they can be complex, i.e. they may consist of several different computational tasks,

- they have to react within precise time constraints to their environment, i.e., they are *real-time* applications.

Supporting the design of such characterized embedded applications for execution on RHD platforms is the aim of this thesis.

### 1.1 Motivation to Real-Time Multitasking

Multitasking is useful if the application is composed of several well separated computational tasks that should be processed quasi simultaneously on limited hardware resources. The concept of multitasking, in combination with the corresponding operating system (OS) support, enables efficient *sharing of resources* due to adequate task scheduling, allows *dynamic changes* of the application due to introduction of new tasks during runtime and greatly *simplifies application development* since tasks can be developed quite independent from each other.

As further motivation, we list several example tasks with real-time constraints which appear in real-world applications. Most of the mentioned applications come from the automotive domain. Some refer to only conceptual systems and some to existing implementations.

- **Engine control system:** A task controlling the engine such as the gas injection and ignition process. Indeed this task may include several sub-controller tasks. The computation of these sub-tasks is based on the cyclic evaluation of the differential equation systems of the corresponding mechatronic controllers. Kopetz describes such example controller in [64] p. 22.

- Vehicle cruise controller: In [8], Axelsson from Volvo Technological Development describes a case study of an advance cruise controller for cars. It keeps the car at a desired speed, but also uses a forward looking radar to avoid collisions with obstacles. The system is composed of several tasks, such as: wheel-speed measuring; speed control which adapts the speed to the desired value; driver-interaction

which checks for break and throttle pedals; *obstacle-detection* which looks for obstacles ahead; *brake-control* and *throttle-control* which perform deceleration and acceleration.

- **Radar system:** Several upper class cars use a radar system for measuring the distance to the cars driving ahead [32]. Such long distance control is used by the cruise control. The implementation of radar signal processing on FPGAs is issued in [6].

- **Camera driving assistance:** The company MobilEye[1] develops several car driver assistance applications based on camera image processing, among them *pedestrian* detection, headway monitoring and warning, forward collision warning, night vision and many more [54]. For the detection of lane marks and vehicles, images are processed through a chain of various processes: 1. selecting candidate regions of interest, 2. single frame classification, 3. multi-frame approval and 4. range measurement. To achieve the required real-time image processing performance of 30 frames per second, the company developed a system on chip (SoC) which hosts two RISC processors and dedicated video processing units and runs at 120 MHz.

All of these tasks have a couple of common features. They are based on computations which can be efficiently implemented on RHDs, have to be evaluated periodically, and are subject to hard real-time constraints. Such systems are targeted within this thesis.

#### Challenges

When designing embedded systems, a key challenge is to implement all required functionalities, meet the required performance and time constraints, but at modest cost. Hence, the system resources have to be used efficiently. For processor based systems, operating systems support resource sharing via multitasking, and appropriate scheduling algorithms ensure the efficient utilization of shared resources while meeting all real-time constraints.

The more reconfigurable architectures push into embedded systems and take over computations formerly implemented on processors or in application specific integrated circuits (ASICs), the more important it becomes to apply the same techniques to RHDs in order to use their resources efficiently. RHDs increase the existing challenges in the following three ways:

1. Design of novel reconfigurable architectures: Most of today's available commercial reconfigurable architectures support dynamic reconfiguration only in a limited fashion. The reconfiguration time of FPGAs ranges from some hundred microseconds to tens of milliseconds, which makes runtime reconfiguration infeasible for applications requiring very short response times. Also partial reconfiguration, which allows reconfiguring a part of the device resources for a new task while other parts keep executing other tasks, has only limited support. Moreover, the architectures do not provide native support for storing and restoring the state of a task before / after interruption, which is a requirement for preemptive multitasking.

Much promising research is currently being performed to overcome these drawbacks, including coarse-grain RHDs and other devices with multiple configurationcontext memories on chip [96][31][50] (see Section 2.1).

2. Runtime environments for reconfigurable devices: Multitasking on RHDs requires some kind of support from a runtime or operating system, similar to an OS for processor based platforms. Such a system needs to manage the RHD resources, control the execution of hardware-tasks and control the device reconfiguration at runtime. Moreover, such an OS has to provide programming interfaces for the application developer to abstract details from the underlying hardware.

Several prototypes of operating systems for FPGAs have been developed by research groups, but still are far behind their counterparts in the processor world [102][57][105][85].

3. Task scheduling and placement: Scheduling and placement methods are required, which allow the OS to efficiently utilize RHD resources for the application tasks and, if needed, deal with real-time requirements. Since the task and resource models of single- and multiprocessor systems are different from those of reconfigurable devices, their scheduling methods cannot be directly applied for RHDs. Moreover, tasks scheduling for RHDs under real-time constraints has been rarely addressed by researchers (e.g. in [80][90]). Scheduling problems for RHDs are much less understood and only a few proposed scheduling approaches exist compared to the classical scheduling problems for processor and multiprocessor platforms.

Hence, there is a considerable need for research in this area in order to catch up with the state of the art of scheduling methods for processors.

### 1.2 Contribution of This Thesis

The main contributions of this thesis are related to the third challenge mentioned above, namely *(real-time)* scheduling methods for reconfigurable architectures. For the well known problem of scheduling periodic real-time tasks, we present one of the first work considering runtime reconfigurable architectures. Three basic scheduling methods are developed and evaluated. Two are driven by the basic (multi)-processor scheduling methods and the third is specially designed for devices without partial reconfiguration support.

A second contribution is given in the area of operating systems for reconfigurable architectures. As a proof of concept, a prototype of an *FPGA based real-time kernel (FBRK)* has been implemented. In contrast to other work, it is completely implemented in (reconfigurable) hardware and designed for full- rather than partial reconfigurable devices. It implements the developed scheduling strategy for devices without partial reconfiguration support and hence is suitable for a wide range of today's devices and platforms.

The contributions in the field of real-time scheduling methods are described more precisely in the following list:

- A new task and resource model for reconfigurable architectures as a generalization of a simple multi-processor model, and definition of the periodic real-time tasks scheduling problem within this context. For this problem, we introduce three independent scheduling strategies based on global scheduling, partitioned scheduling and server based scheduling. We develop a linear-time scheduling test for the global scheduling strategy, and introduce and analyze optimal and heuristic algorithms for the partitioned scheduling and server based scheduling strategy.

- The performance of all three strategies is compared analytically and by simulation studies. We show that the three approaches do not dominate each other in performance. Simulation results show, that for many cases the *global scheduling* strategy achieves high device resource utilization of over 90% and outperforms the *partitioned scheduling* strategy. In contrast, when a scheduling test is required to predict that no deadline will be missed, significantly higher resource utilization is achieved by the *partitioned scheduling* strategy compared to the *global scheduling* strategy.

As the reconfiguration time cannot be neglected, the associated overhead is included within the analysis of all three strategies. Main results state that the overhead is bounded and in many cases stays reasonably small, if the device configuration time is less than 10% of the runtime of the shortest task. Furthermore, the *partitioned scheduling* and *server based scheduling* methods suffer much less from this overhead than the *global scheduler*.

• In order to deal with the specific characteristics of hardware tasks and reconfigurable platforms, we generalize and extend our model. The first generalization allows considering tasks, for which not only one but several alternative circuit implementations exist. For such applications, the optimal variant selection is computed by integer linear programming, which improves considerably the performance of the *partitioned scheduler* compared to tasks without variants.

Secondly, we extend our model to consider tasks' memory usage under real-time constraints. We present a method to efficiently share memory banks of the plat-form among tasks without jeopardizing task deadlines.

In summary this thesis presents a foundation for real-time multitasking on RHDs, presenting the models, algorithms, analysis and a prototypical implementation.

### 1.3 Chapter Outline

The thesis has the following organization:

Chapter 2 *Background and Related Work* provides a background to this thesis and summarizes the related work. It discusses the different kinds of reconfigurable hardware architectures that we consider as processing devices throughout this work. The concept of hardware-tasks is introduced and previously reported multitasking models for such tasks are reviewed and classified. Finally, the chapter presents related work in real-time

scheduling, including single and multiprocessor scheduling algorithms for periodic tasks and the few research on real-time scheduling for RHDs.

Chapter 3 *Problem Modeling and Metrics* introduces the task and resource models and the basic notations used within this work. The general problem of scheduling periodic real-time tasks onto an RHD is defined.

Chapter 4 *Three Scheduling Algorithms* presents our main methods to schedule periodic task onto RHDs, namely global EDF scheduling, partitioned EDF scheduling and server based scheduling. The scheduling conditions and basic analysis are developed.

Chapter 5 *Comparison of Algorithm Scheduling Performance* evaluates the quality of our three proposed methods. Only the pure scheduling performance without considering any reconfiguration overhead is compared. The first part presents an analytic comparison and derives qualitative statements. The second part presents results from numerous simulation experiments, showing how the algorithms perform in average.

Chapter 6 *Execution Model and Overhead Analysis* goes away from the idealistic task model and accounts for execution time overheads. For each scheduling method a suitable reconfiguration model and its runtime system requirements are described. The time overhead resulting from device reconfigurations is included in the scheduling conditions of each algorithm. Finally, the results from simulation experiments on the algorithm performance including overheads are shown.

Chapter 7 *Model Extensions* takes special characteristics of hardware-tasks into account. A first part presents methods for a generalized task model that allows specifying not only one but several implementation variants per tasks - each with a different area and computation time. The second part captures the memory requirements of hardware-tasks. A method for sharing physical platform memories between parallel executed task is shown which has the potential to considerable reduce the memory requirements.

Chapter 8 *Prototype: FPGA Based Real-Time Kernel* describes our realization for the server based scheduler. The system architecture and an automated synthesis flow are described. Finally, results on the logic requirements and timings are reported.

Chapter 9 *Conclusion and Outlook* finalizes the thesis with a summary, draws conclusions and presents suggestions for future research.

# CHAPTER 2

## Background and Related Work

This chapter provides a background to this thesis and summarizes the related work.

The first section discusses the different kinds of reconfigurable hardware architectures that we consider as processing devices throughout this work. It gives a background to fine and coarse grain reconfigurable devices, the different reconfiguration modes and discusses the architecture of typical embedded systems based on such devices. Since reconfigurable devices and computing systems have been surveyed several times (e.g. in [31] p. 11 ff.), we keep this section therefore small.

In Section 2.2, we briefly introduce the concept of hardware-tasks, which refers to computational tasks implemented as digital circuits for execution on an RHD. By means of an example of a hardware task, several characteristics such as resource requirements and execution times are discussed.

The third section concentrates on multi-tasking on reconfigurable hardware. In order to be able to develop a reasonable task and resource model for our work (Chapter 3), six different device resource sharing models, that have been used in the literature, are discussed and classified (Section 2.3). We clear out why only two of the six models will be considered in our scheduling approaches. Afterwards, we present related work that has specifically targeted the problem of scheduling tasks on RHD architectures. While this documents the attraction of the research field, it shows that most work does not consider tasks with real-time constraints. Finally the section closes with a brief description of projects that have implemented reconfigurable systems supporting hardware multitasking. It shows that various prototypes exist, which support execution environments as they will be assumed in our task and resource model of Chapter 3.

The last part of this chapter presents related work in real-time scheduling (Section 2.4). We introduce the periodic task model and clarify its importance, since it is used as a basis for our task model. Furthermore, we present the basics of single processor scheduling algorithms, since they are also fundamental to all scheduling methods for parallel archi-

tectures. Scheduling methods for multiprocessors are discussed in more detail, since the multiprocessor model is closely related to our RHD resource model and, furthermore, the basic techniques of multiprocessor scheduling have been inspired two of our three scheduling methods which will be introduced in Chapter 4. Finally, we close with the few work considering real-time scheduling for RHDs or similar architectures. We conclude, that the problem considered in this work is actually novel, but as well a straight forward extension of the basic single- and multiprocessor scheduling problems. Furthermore, the approaches we use are based on scheduling methods with strong foundation in literature.

### 2.1 Reconfigurable Hardware Devices

This section gives a background on different types of *reconfigurable hardware devices* (RHD), their inner architecture and how they are used to implement computations.

The most prominent type of RHD is the field-programmable gate array (FPGA). It was invented in the eighties and is a further development of early programmable logic devices. Even if the FPGAs where mainly invented for prototyping of digital circuits and for implementing glue logic, researchers got attracted by the feature of runtime reconfiguration (or runtime reprogramming) of these devices, which allows general FPGA based computations. Since then, the research field *Reconfigurable Computing* [31][46] was born, which focuses on new RHD based computing paradigms beside the Von Neumann paradigm as well as on the invention of new RHD architectures to overcome the drawbacks of commercial available FPGAs.

First we will take a closer look to the architecture of RHDs which can be classified into *fine-grained* architectures, which are basically FPGAs and *coarse-grained* architectures, which are mostly academically proposed devices or prototypes from startup companies.

### 2.1.1 Fine-Grain RHDs (FPGAs)

The term *fine-grain* is used to denote devices, which can be configured on bit-level. We use *fine-grain RHD* as a synonym for FPGA.

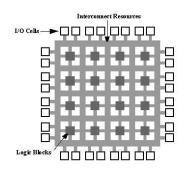

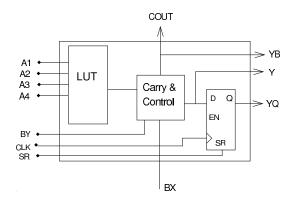

The basic architecture of today's FPGAs is shown in Figure 2.1 and consists mainly of an array of programmable *logic blocks*, programmable *interconnect* as well as general purpose *input output cells*. The logic blocks can be configured to implement small logic functions and registers, which can be composed to larger digital circuits by the programmable interconnect. A typical structure of a logic block is shown in Figure 2.2. Its main components are *look-up tables* (LUTs) to implement combinatorial logical and flip flops to implement storage. An *n* input LUT is an *n*-address memory, which can store the  $2^n$  possible values of a Boolean function with *n* input variables. To implement a specific Boolean function, the LUT is programmed with the function's truth table. The input values are used to address the LUT and the data output represents the value of the function. The output of the LUT is either fed into a flip flop of the logic block or directly

Figure 2.1: Basic structure of an FPGA

connected to the logic block's output. Typically, 4-input LUTs are used, since many studies show that they present a good tradeoff for most digital designs [2]. Recently, Xilinx switched from 4- to 6-input LUTs in their latest Virtex-V architecture [33]. Altera uses in their Stratex-II architecture adaptive logic modules with a configurable LUT size, which can be used e.g. as one 7-input LUT or as two 4-input LUTs [3].

The flip flops of the logic blocks are used to implement the storage registers inside a digital design. They are connected to a global clock network and support features like synchronous or asynchronous reset.

The programmable interconnect consists of configurable crossbar switches, which allow establishment of connections between outputs and inputs of the logic blocks as well as to the I/O cells.

Also these elements are all what is needed to implement a digital design, modern FPGAs include many more types of resources to achieve better performance and efficiency. Typical resources of the market leader FPGA vendors are briefly described below.

**Block RAMs** are dedicated blocks of static RAM of medium size (typical with a size of 18 kBit), which can be used to store larger amounts of data onto the device. In contrast to flip flops which can be accessed independent of each other, the data

Figure 2.2: Structure of FPGA logic block (source: [106])

of each block RAM memory may only be read or written sequential on a word by word basis. (Some devices provide dual ported block RAM.)

- **Carry logic** is a special logic inside the logic blocks to forward carry bits to improve the performance of arithmetic functions such as adders.

- **DSP cores** are dedicated functional units like multiplier and multiply-accumulate structures to improve the performance of digital signal processing functions.

- **Processor cores** are dedicated microprocessor cores hosted on the FPGA chip. They are used for complex system-on-chip designs which include software and hardware parts.

- **High speed I/O transceivers** are dedicated transceiver circuits which implement several high speed I/O standards to enable serial I/O of several GBit per second.

- **Clock managers** are units, which allow generating and distributing clock signals with minimal skew throughout the FPGA chip. Modern FPGAs support multiple global clock networks enabling multi clock designs.

- **Tri state buffers** are components, to support on chip communication bus systems with multiple clients.

FPGAs are typically programmed using an ASIC-like design flow. Design entry is usually provided in a hardware description language like VHDL or VeriLog. The design flow includes the synthesis of the design into a net-list, mapping the net-list to the components provided by the FPGA and a place and route step, in which components are allocated to specific FPGA resources and connected via the configurable interconnect. Based on the result a programming file for the FPGA, also called a bit-stream, is generated which can be directly downloaded into the FPGA configuration memory.

#### 2.1.2 Coarse-Grain RHDs

Like FPGAs, coarse-grain RHDs are based on an array of programmable logic blocks called *processing elements* and *programmable interconnect*. In contrast to the fine-grain FPGAs, coarse grain RHDs provide programmability on word-width level of e.g. 8, 16, 24 or 32 bits [50][35][56][13]. The processing elements are not based on LUTs anymore, but provide arithmetic operations like addition, multiplication and shift on word level operands. Therefore, sometimes these devices are referred to as ALU arrays. The LUT approach, which allows the implementation of general functions, is not feasible on word width level: Imagine a processing element with two 16-bit inputs and one 16-bit output. Enabling programmability of a general logic function would require 16 times a 32-bit input LUT which results in  $16 \times 2^{32}$  bit = 8 GB of memory for each processing element.

The operation on word-width level gives the coarse-grain RHDs several advantages compared to FPGAs: The arithmetic functions are implemented as dedicated circuits, which makes them much smaller in terms of chip-size and faster than functions implemented on FPGA logic blocks. Also the crossbar switches become simpler, as not single signals but entire buses of signals are connected at once. Since a coarse-grain RHD consists of much fewer processing elements than an FPGA of comparable chip size, the configuration memory is dramatically reduced. E.g. to program the device to implement a 16 bit multiply-accumulate unit, only two processing elements and the crossbar in between have to be configured, compared to tens or hundreds of logic blocks and crossbars that have to be configured when the same function is implemented on an FPGA. This reduction of configuration memory is directly translated to higher reconfiguration speed. Typically, coarse-grain devices can be reprogrammed several times as fast as FPGAs.

The coarse-grain RHDs gain these benefits at the cost of sacrificing some flexibility, which makes them inefficient when the problem does not mainly consists of word-width arithmetic operations. For example an *add* operation of 3-bits operands could occupy an entire 32 bit processing element.

#### 2.1.3 Configuration Memory and Reconfiguration

The current function and behavior of the RHD is determined by the content of its configuration memory. This memory consists of static RAM memory cells, which are distributed on the device array. For each logic block of an FPGA, there are configuration memory cells storing the content of the LUT, the information about how the flip flop is connected, its initial state and its reset mode. The configuration memory of the processing elements of coarse-grain devices basically determines the function of the ALU. The configuration memory of the crossbar switches determines the connections of the logic blocks or processing elements inputs and outputs to routing channels as well as which horizontal and vertical routing lines are connected.

Since the configuration memory consist of SRAM cells, it can be programmed arbitrarily often, which does not only allows the definition of the function of the RHD after the chip production, but also changing it online during runtime. Therefore, we distinguish between *static* configuration and *dynamic* reconfiguration. Moreover, some RHDs allow reprogramming some parts of the configuration memory and therefore to change the functionality of only some logic blocks or processing elements respectively, while others keep operating. Therefore, we distinguish between *full*- and *partial* device reconfiguration.

#### Architecture of Configuration Memory

For physical reasons, the SRAM cells of the configuration memory have to be local to the elements they are configuring.<sup>1</sup> A simple and area efficient method to make the configuration memory accessible from outside the device is to connect all its cells to a long shift register. The RHD can be reprogrammed by sequentially shifting new configuration bits into the configuration memory until the entire device is reconfigured. Obviously this addressing schema allows only full configuration and the device cannot be used during the time of the reconfiguration process. Also the reconfiguration time is

<sup>&</sup>lt;sup>1</sup>It is inefficient in terms of path delay and chip area to rout long connection lines between configuration memory cells and the elements to configure.

very long, since only 1-bit per clock cycle can be written.

These drawbacks can be overcome by a more sophisticated configuration memory architecture. The width of the configuration interface can be enhanced, which allows to reprogram several bits in parallel. The configuration memory can be made partial accessible by allowing addressing certain portions of it at the cost of extra chip area for address decoding. For example the FPGAs of the Xilinx Virtex and VirtexII families allow reprogramming entire columns of logic blocks, which allows a partial reconfiguration of the FPGA at a rather coarse level.

Reconfiguration times of coarse-grain reconfigurable architectures are typically much shorter than that of FPGAs, since they have less cells and hence a much smaller configuration memory. A further approach to overcome the long reconfiguration time are *multi-context* devices [31][35][96]. These devices have not only one but some few configuration memories for all device resources on chip. While this adds considerable cost in terms of chip area, it allows changing from one configuration to another within few clock cycles.

Within our resource model of Chapter 3 we consider only the homogeneous cells of an RHD and neglect additional resources such as I/O pins, DSP functions and embedded microprocessors. How such additional resource can be included within our model and our scheduling methods will be discussed in the future work section of Chapter 9. Dedicated memory blocks of the RHD and external SRAM banks are considered in our extended model of Section 7.2.

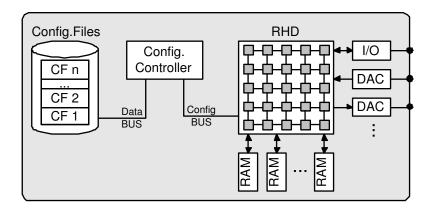

### 2.1.4 Architecture of RHD Based Computer Platforms

By the term RCP (*RHD based computer platform*) we denote an embedded computer system, whose main computational resources consist of RHDs (see Figure 2.3). The main computational tasks of the applications are executed on the RHD, e.g. by programming the device with digital circuits compiled as FPGA configuration bit-streams. Microprocessors are optional and their usage is not given special consideration within this thesis. However, microprocessors may be included within the system as separate chips external to the RHD, or integrated as dedicated circuits within the RHD (e.g. Xilinx VirtexII Pro [108]) or as soft core CPUs<sup>2</sup>, which are implemented out of RHD logic cells (e.g. the Xilinx Microblaze or the Altera NIOS).

Beside the RHDs, the system includes memory to store the RHD programming data as well as application data and peripheral I/O devices to communicate with the environment. Additionally, a device controlling the reconfiguration process of the RHD is included. Concrete examples for FPGA based reconfigurable computing platforms are the RC100, RC200, RC300 from CELOXICA [27], the XF-board [98] from ETH Zurich, the Erlangen Slot Machine [20], or development boards distributed by XILINX. Some platforms are module based and can include several FPGA such as the RAPTOR 2000 system [62]. An example of a system including a coarse-grain RHD is the DAPDNA-EB4

$<sup>^{2}</sup>A$  soft core CPU is a CPU which is implemented as FPGA design.

Figure 2.3: Architecture of an RHD based platform

board of the IPFlex company, which includes two DAPDNA-2 reconfigurable processors consisting of 376 processing elements each [56].

As for the memories, the platforms typically host several SRAM (static RAM) banks which are directly connected to the RHD. They are used to store processing data to which relatively fast access with predictable timing is required, but which is too large to be stored in on-chip memories. Additionally non-volatile memory such as flash memory is included to store the configuration data (programming files) and other persistent data. Larger but slower DRAMs (dynamic RAM) are included to store large blocks of application data, which is accessed with subject to weaker timing constraints.

RCPs often have a wide set of peripheral I/O. This includes for example digital-analog and analog-digital converters, video and audio interfaces such as S-VIDEO or VGA, standard interfaces like PS2, USB, fire-wire, network interfaces such as Ethernet or CAN, and user definable digital I/O.

In the models and methods used in this thesis we abstract from platform details and consider as platform resources only the logic blocks or processing elements of the RHD, the internal and external SRAM memory banks, the memory hosting the RHD configuration data as well as the bus connections between these resources. We neglect several additional resources and details for the following reasons:

- Details have to be abstracted, to keep the model valid for wide class of RCPs from different vendors as well as to keep the model complexity low.

- Microprocessors are not included within the model, since we assume they are used only for controlling the execution and reconfiguration of the RHD, not for executing the application tasks themselves. Such hybrid systems, which couple microprocessors with RHDs and use both for computation (e.g. [56]) open the issue of hardware–software co-design[92][75]. That is another independent research field and its topics are not addressed within this thesis.

- An RCP according to our model has only one RHD. From a practical point of view, multiple RHDs appear mostly in high-performance computing systems such

as Cray's XD1 [34] with the aim to get highest computational power at any price. In contrast, in embedded system design the challenge is rather to choose from the wide range of different size RHDs the smallest one that satisfies the application requirements.

From a theoretical point of view, multiple RHDs open issues which are stronger related to parallel processor systems than to the special characteristics of RHDs. Such issues are for example clustering and partitioning of applications and localization of communication, which have been exhaustively studied for multiprocessors but are not addressed within this thesis.

### 2.2 Hardware Tasks

In our application model of Chapter 3 and later on in the enhanced application models of Chapter 7, we will make several assumptions for the characteristics of application tasks. To give a better idea of what kind of tasks we consider and to show that the assumptions we make are reasonable, this section presents a short case study of an image processing task based on *Discrete Cosine Transformation (DCT)* computations.

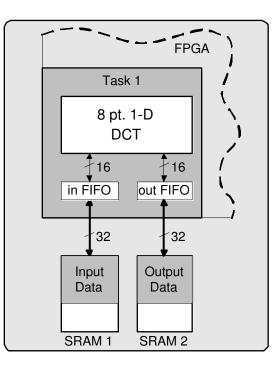

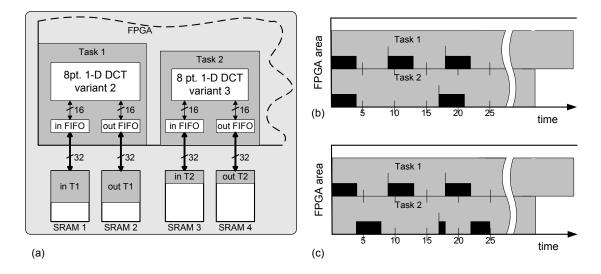

**Example 1.** We assume an image processing system which includes a task that computes the DCT coefficients of the rows of an image. The data to be processed has a fix size of N samples, each coded by 16 bits on which an 8 point one dimensional DCT should be performed.

Figure 2.4: Example of a DCT task on platform

Figure 2.4 illustrates how this task is realized on an FPGA based platform. Since the image data may be too large for FPGA internal block RAMs, the N input samples as well as the output coefficients to be computed are stored in the external SRAM banks 1 and 2 respectively. For the actual DCT computation a XILINX 1-D DCT IP-core [107] is used. Since the external RAM banks have a word width of 32 bits but the samples are 16 bit values, input and output FIFOs<sup>3</sup> are introduced to buffer the input samples and the produced output coefficients respectively and to convert between the 32 and 16 bit words.

| variant | FPGA area | throughput   | ext. RAM port access |                         |         | exec. time |

|---------|-----------|--------------|----------------------|-------------------------|---------|------------|

|         | (slices)  | (sample/clk) | period               | amount                  | utiliz. | N=1024     |

| 1       | 982       | 1            | 2 clks               | $1 \times 32$ bit word  | 50%     | 1028 clks  |

| 2       | 767       | 8 / 9        | 9 clks               | $4 \times 32$ bit words | 45%     | 1185 clks  |

| 3       | 589       | 8 / 17       | 17 clks              | $4 \times 32$ bit words | 24%     | 2232 clks  |

Table 2.1: Size, throughput and memory access pattern of several variants of a XILINX 8 point 1D-DCT IP core [107].

As reported in the DCT IP-core data-sheet [107], the designer can choose between several implementation variants with a trade-off between FPGA area and throughput as shown in Table 2.1. To guaranty that the DCT core can achieve these throughput values – which is mandatory for real-time processing – the FIFOs have to be chosen of appropriate size and a certain access rate to the external RAMs has to be guaranteed. The required access rate to external memory is reported in the middle column of Table 2.1. E.g. variant 1 processes one 16-bit sample per clock cycle. Therefore, within a period of 2 clock cycles the task reads one 32 bit word from SRAM1 into the input FIFO. In contrast variant 3 has a throughput of 8/17. Hence it reads within a period of 17 clock cycles 4 data words from the external RAM. Note that since a FIFO buffers the data it does not matter in which exact clock cycles the data is read from the RAM - as long as 4 words within a period of 17 clocks are read.<sup>4</sup> Thus, the RAM access pattern of the task has the nature of periodic real-time access: At the beginning of a period it requests to read/write a certain amount of data from/to the external RAM bank into/out of the FIFO. The deadline for this transaction is the beginning of the next period to prevent an underflow or overflow of the FIFO buffers.

The total worst case execution time of the DCT example task is computed using Equation 2.1. Beside the internal latency of the DCT core, two times the RAM access period is added to account the initial filling of the input FIFO and the final deflating of the output FIFO.

$$exectime = \frac{N}{throughput} + DCT latency + 2 \times RAM access period$$

(2.1)

For a data size of N = 1024 samples, the execution time according to Equation 2.1 for

$<sup>^3 {\</sup>rm first}$  in first out buffers

<sup>&</sup>lt;sup>4</sup>The same rates apply for the write access to the SRAM2.

each of the three variants of the task is reported in Table 2.1 as well.

This case study of a DCT task showed that it is reasonable to assume application models where tasks have the following characteristics:

- Tasks may be realized as various implementation variants with different performance vs. RHD-resource tradeoffs. Such various implementations can be achieved by considering different circuit architectures. For example, a multiplication can be realized by a bit-serial or a bit-parallel architecture, hence resulting in a small but slow and in a fast but large circuit.

- A task variant requires a specific amount of RHD resource. For FPGA devices, the synthesis tool typically provides information on how many FPGA slices are required by the design. Often, slice resources are further distinguished to the number of required LUTs and flip flops. Additional resources are reported as well, such as the required block RAMs, or multiplier cores. Hence, the basic resources can be captured by a scalar value (e.g. number of FPGA slices) or by a resource vector.

- A task variant may have a known execution time which is usually given by the number of required clock-cycles divided by the clock-frequency at which the task is executed. Determining the worst case execution time of a hardware task is discussed in the next paragraph.

- A task may require external memory to store larger amounts of data and may access it periodically within hard real-time constraints.

These assumptions are the motivation for our application models used within this thesis, namely the basic periodic real-time tasks model, introduced in Chapter 3, and the model extensions by task variants and periodic memory access, introduced in Chapter 7.

#### Worst Case Task Execution Time

Determining the execution time is often not as easy as it has been for the DCT task of the example above and a deeper analysis is required. Without knowledge on the tasks' execution times we cannot develop a scheduling strategy, which allows us to guaranty that a task will finish before some given deadline. Moreover, in order to guaranty hard deadlines of tasks we have to design the system for peak load situations; even if in average the load of the system is low. Hence, we would like to know an upper bound on the execution time for each task. This is done by a so called *worst case execution time* (*WCET*) analysis, which is another research field within real-time systems and out of the scope of this thesis (see e.g. [64] p.86ff. and [24]p.411ff.). Rather we briefly discuss the issues of WCET analysis of hardware tasks executed on reconfigurable architectures compared to software tasks running on CPUs.

The WCET is mainly influenced by the *program flow* of the task itself and the *micro architecture* of the machine executing the task.

**Program flow:** To determine the WCET, the first step is the analysis of the program flow of the considered task. Usually, it is described by directed graph models capturing the sequential basic blocks and control decisions. Once the computation times of the basic blocks are known, the directed graph can be collapsed. For example a branch is collapsed to one node by assigning the WCET of the longer path. Loops are replaced by accounting n times the WCET of the body, where n is the bound on the number of loop iterations (loops must be bounded to have a bounded WCET of the task).

In general, the program flow analysis is independent of whether the task is implemented as hardware or software, but the high amount of concurrency in hardware tasks might make their analysis more challenging. However, many applications considered for the execution on reconfigurable hardware are data flow dominated, such as signal processing tasks, filters, coders and decoders. Due to few control decisions, such tasks are often simpler to analyze than arbitrary tasks.

**Micro architecture:** The WCET of the task's basic blocks can be derived by accounting the time required by the clock cycles in case of hardware tasks or by the instructions in case of software tasks.

Unfortunately, determining the time for an instruction on modern CPUs can be quite difficult. The data and instruction cache of processors provide enormous speedups when fetching instructions and accessing data, but this is transparent to the programming model. To be able to account these speedups when computing the WCET requires a detailed analysis of the program code together with the cache model, in order to know which items can be guaranteed to be inside the cache and which not. This becomes even harder, when a task can be interrupted by another task which might overwrite some cache values. Also the pipelined execution of instructions does not provide guaranteed performance, since we have to consider pipeline stalls.

In case of a hardware task, the programming model (i.e. VHDL) does not abstract from platform details that influence the number of clock cycles required by a basic block. Often this number can be directly achieved from the register transfer level (RTL) description, or results from the scheduling phase of high level architecture synthesis. In other cases, the vendor of an IP-core reports on the required clock cycles in the according data-sheets. The maximal clock frequency is reported by the place and route tools for a specific target device.

We can conclude that for many hardware tasks of our interest, obtaining the WCET is not a major issue. Analyzing the WCET for arbitrary hardware tasks might be yet another research topic.

### 2.3 Multi-Tasking on Reconfigurable Hardware

This section presents an overview of work in the field of *RHD based multi tasking*, which is directly related to this thesis. Additional work, which includes models and methods that are related to- or applied within the methods of this thesis, is introduced in the following chapters.

We categorize different models of RHD based multitasking that have been proposed in related work. The related systems can be classified according to the following properties:

- **RCP Architecture:** Existing or proposed systems are either based on single RHDs, based on multiple RHDs or are hybrid systems coupling microprocessors with RHDs.

- **RHD Resource Sharing Model:** Many approaches exist on how systems allow multiple tasks to share the RHD resources. The most relevant are discussed in detail in Section 2.3.1.

- Task execution model: The system may or may not allow preemptive multitasking.

- **Application model:** It can be distinguished between *off-line* and *online*-problems. In the first case, the entire application parameters such as the tasks and their arrival and execution times are known at design time. For example the application to be scheduled for execution is modeled in the form of a directed acyclic task-graph. Typical optimization goals are to minimize the overall execution time or to minimize the required resources, i.e., the size of the RHD. In *online*-problems, application parameters such as the tasks and their arrival times are determined at runtime. Therefore the system has to determine at runtime, which resources are assigned to the tasks without knowing which tasks have to be executed in the future. A typical optimization goal in this scenario is to minimize the average response time of tasks.

#### 2.3.1 Resource Sharing Models

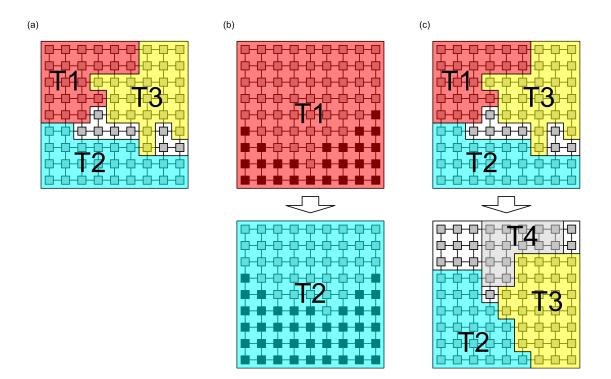

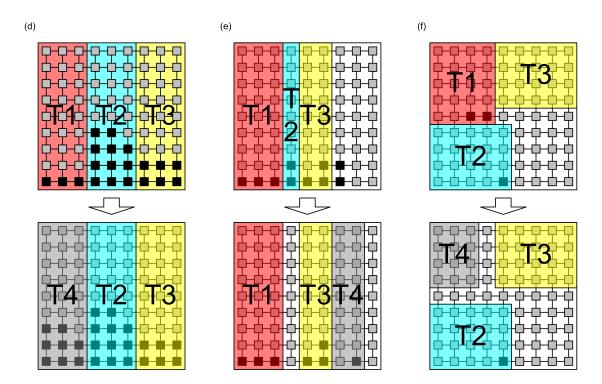

There exist numerous approaches how multiple tasks share the resources of an RHD. These are sometimes closely related to the supported reconfiguration features of the devices, i.e. if the RHD supports unrestricted partial, column-wise partial or only full reconfiguration. We describe six models; models (a) to (c) are based on full device reconfiguration and models (d) to (f) are based on partial reconfiguration.

(a) Static Partitioning: If multiple tasks have to be processed by one RHD, today's practice would be, using the static assignment partitioning approach, which is illustrated in Figure 2.5-(a). All system tasks are integrated within one RHD configuration, which is loaded to the RHD while the system is booting and stay active until the system shuts down. In this approach, the RHD behaves similar to an ASIC. The required size of the RHD is determined by the sum of the resource

Figure 2.5: RHD Resource sharing approaches based on full RHD configuration.

requirements of all tasks. Since no timesharing of RHD area takes place, task scheduling and sophisticated resource management methods are obsolete. This greatly simplifies the system implementation. This approach is efficient when most of the tasks need to be running most of the time. It becomes ineffective when some tasks have to be executed just once or only sporadically from time to time, since all existing tasks allocate resources no matter whether they are running or not.