### PADERBORN UNIVERSITY

DISSERTATION

## Efficient Parallel Branch-and-Bound Search on FPGAs Using Work Stealing and Instance-Specific Designs

*by* Heinrich Riebler

A thesis submitted in fulfillment of the requirements for the degree of Dr. rer. nat.

in the

Faculty for Computer Science, Electrical Engineering and Mathematics

Gewidmet meinen Eltern, in Dankbarkeit und Liebe.

## Acknowledgements

I would like to thank:

- My supervisor Prof. Dr. Christian Plessl. This work would not have been possible without your professional and personal support during the last years.

- Prof. Dr. Marco Platzner for serving as a reviewer for this thesis.

- Prof. Dr. Friedhelm Meyer auf der Heide, Prof. Dr. Kevin Tierney and Dr. Theodor Lettmann for serving on the oral examination committee.

- All colleagues from the High-Performance IT Systems research group, the Paderborn Center for Parallel Computing and the SFB 901 – On-The-Fly Computing. A warm thanks goes to Gavin Vaz, Tobias Kenter and Achim Lösch for intensive collaborations on joint projects.

- A special thanks goes to Michael Laß, Robert Mittendorf and Thomas Löcke, who directly contributed to my research covered in this thesis as Master students or student assistants I have supervised. It was a pleasure to work with you.

These acknowledgments would not be complete without thanking my family for their unconditional support: first and foremost, Lina, Mael and our little son on the way. Furthermore, I would like to thank my parents, my sister, my brother and all members of my family-in-law.

## Abstract

In recent years, increasing technization and market analysis purposes have resulted in more and more data being generated. The growing need of data analysis and processing has become omnipresent for many combinatorial optimization or planning problems. To take advantage of the promises of the digital age, efficient search algorithms and their efficient implementations in terms of performance and energy efficiency are important. Only the combination and fine tuning of efficient algorithms *and* their efficient implementation on suitable platforms can lead to a high performance and low energy consumption.

One of the most common methods for processing such very large search spaces is using branch-and-bound (B&B) search algorithms. B&B search algorithms are highly relevant because they are used to solve many real-world operational problems (e.g. production and personnel planning, scheduling, complex decision processes, etc.). The search space in branch-and-bound searches is organized in a tree data structure and the algorithm tries to eliminate infeasible solutions as early as possible by pruning unpromising subtrees through a bounding function. Since these excluded subtrees no longer have to be considered, the computing effort is reduced considerably in some cases.

In this thesis, we study the insufficiently understood efficient realization of branch-and-bound algorithms for field programmable gate arrays (FPGAs). FPGAs are integrated circuits consisting of programmable logic blocks and programmable interconnects that can be specialized for specific applications after manufacturing the chip. Branch-and-bound problems are inherently difficult and not the typical class of problems that have been tackled using FPGAs, because they are control-driven and not data-driven. On the other hand, FPGAs have proven to be highly efficient in terms of chip area, power consumption and performance for a wide range of other suitable application domains. In this thesis, we bridge this gap and show that custom hardware designs can significantly accelerate the execution of these algorithms. First, we identify general elements of B&B algorithms and develop and demonstrate their efficient implementation as a finite state machine on FPGAs. Our architecture shows trade-offs between highly optimized combinational datapaths for the performance-critical parts of the search tree and more resource-efficient pipelined ones for the less frequent and more complex parts.

Then we extend our design with two optimization techniques to further improve the efficiency. For the first optimization we introduce the concept of hardware workers that autonomously cooperate using work stealing to allow parallel execution of branch-and-bound algorithms and full utilization of the target FPGA. The hardware workers dynamically share and balance their work and show near linear speedups. For the second optimization we explore the advantages of instance-specific designs for B&B algorithms that target a specific problem instance to improve performance and combine them with the design using work stealing. The instance-specific design utilizes the high potential of FPGAs for specialization and custom optimization for a particular problem instance. We present a fully automated generation of customtailored designs that existing tools do not deliver. We demonstrate how instancespecific designs can be generated on-the-fly such that the provided speedups outweigh the additional time required for design synthesis.

Finally, we evaluate all of our approaches and compare each result to those obtained using similar techniques in software. Our results show that our hardware implementation targeting a Maxeler FPGA system can outperform a software implementation while being more energy efficient at the same time.

## Zusammenfassung

Durch die zunehmende Technisierung entstehen immer mehr Daten oder es werden Daten für marktanalytische Zwecke generiert. Entsprechend aufwendig werden Entscheidungs-, Planungs- oder Optimierungsprobleme, deren Ziel darin besteht, eine bestimmte – im Idealfall beste – Lösung in den immensen Suchräumen dieser Daten zu finden. Neben effektiven Algorithmen zur Lösung solcher Probleme spielt deren hocheffiziente Implementierung auf modernen Rechenanlagen eine immer wichtigere Rolle. Von besonderer Bedeutung ist dabei das Verhältnis der Datenverarbeitungsleistung zur elektrischen Leistungsaufnahme. Nur durch die Kombination und Feinabstimmung von effizienten Algorithmen *und* effizienten Implementierungen auf geeigneten Rechenanlagen kann eine hohe Datenverarbeitungsleistung bei geringer Leistungsaufnahme erzielt werden.

Eine der verbreitetsten Methoden, um derartige Suchprobleme effizient zu lösen, ist das Branch-and-Bound (B&B) Verfahren. Branch-and-Bound wird beispielsweise vielfach im Bereich der Unternehmensplanung (z.B. zur Produktions- und Personaleinsatzplanung) und zur Entscheidungsunterstützung bei kombinatorischen Optimierungsproblemen verwendet. Der sich aus der Problemstellung ergebende Suchraum wird beim B&B-Verfahren in einer Baum-Datenstruktur organisiert. Das Verfahren schließt durch schrittweises Verzweigen im Baum (branch) und Begrenzen von Teilbäumen (bound) systematisch Teilbereiche des Suchraums aus, die nicht zu einer gültigen bzw. optimalen Lösung führen können. Da diese ausgeschlossenen Teilbereiche nicht mehr betrachtet werden müssen, reduziert sich der Rechenaufwand teilweise erheblich.

In dieser Arbeit konzentrieren wir uns auf die effiziente Implementierung von Branch-and-Bound Verfahren auf Field Programmable Gate Arrays (FPGAs) für derartig gelagerte Suchprobleme. FPGAs sind integrierte Schaltkreise, bestehend aus programmierbaren Logikbausteinen, die für bestimmte Aufgaben spezialisiert werden können. Branch-and-Bound-Probleme gehören nicht zu den klassischen Problemen, die auf FPGAs untersucht werden, da die Berechnungsvorschrift von B&B-Verfahren kontroll- und nicht datengesteuert ist. Andererseits haben sich FPGAs für eine Vielzahl geeigneter Anwendungsbereiche als hocheffizient in Bezug auf Schaltkreisfläche und Verhältnis von Datenverarbeitungsleistung zur elektrischen Leistungsaufnahme erwiesen. In dieser Arbeit schließen wir diese Lücke und zeigen, dass hochspezialisierte FPGA-Implementierungen die Ausführung von Branch-and-Bound-Algorithmen erheblich beschleunigen können. Dazu identifizieren wir zunächst allgemeine Elemente von Branch-and-Bound-Algorithmen und zeigen systematisch Möglichkeiten einer effizienten Implementierung auf FPGAs mit Hilfe von Zustandsautomaten. Wir untersuchen bei der Auswahl unserer Architektur die entstehenden Kompromisse zwischen hochoptimierten kombinatorischen Datenpfaden für die leistungskritischen Teile des Suchraums und ressourceneffizienteren Datenpfaden mittels Pipelining für die weniger häufigeren und komplexeren Teile des Suchraums. Anhand einer konkreten Fallstudie demonstrieren wir, wie

durch Ausnutzung der architektonischen Merkmale, der Spezialisierung und der unterschiedlichen Parallelitätsstufen von FPGAs eine Auslagerung der Berechnung auf den FPGA zu einer Verbesserung der Datenverarbeitungsleistung führt.

Anschließend erweitern wir unser Design noch um zwei Optimierungsverfahren, um die Effizienz der Ausführung weiter zu steigern. Die erste Optimierung erzielen wir durch die Parallelisierung des Branch-and-Bound-Verfahrens auf dem FPGA. Als Parallelisierungsstrategie verwenden wir Work Stealing, womit die autonome Zusammenarbeit mehrerer Instanzen auf einem FPGA ohne zentrale Steuereinheit ermöglicht wird. Jede Instanz bemüht sich selbstständig um Arbeitspakete, indem sie aktiv Pakete von anderen Instanzen stiehlt. Dadurch werden eine effiziente Arbeitslastverteilung und eine parallele Ausführung des B&B-Verfahrens sichergestellt. Unsere Implementierung ermöglicht die volle Ausnutzung des FPGAs und zeigt nahezu lineare Skalierungseigenschaften, wenn die Taktrate des FPGAs konstant bleibt. Für die zweite Optimierung untersuchen wir instanzspezifische FPGA-Designs, angewandt auf Branch-and-Bound-Algorithmen. Diese zielen darauf ab, besonders schwierige bzw. zeitintensive Probleminstanzen einer Anwendung zu verbessern. Dazu wird die konkrete Probleminstanz analysiert und die konfigurierbare Schaltung speziell auf das konkrete Problem optimiert. Dies demonstriert das hohe Spezialisierungspotential von FPGAs. Wir beschreiben eine vollautomatische Generierung von maßgeschneiderten FPGA-Designs für das Branch-and-Bound-Verfahren und kombinieren diese zusätzlich mit den Parallelisierungstechniken aus der ersten Optimierung.

Schließlich evaluieren wir alle unsere Ansätze und vergleichen jedes Ergebnis mit denen, die mit äquivalenten Techniken bei einer Ausführung in Software auf Central Processing Units (CPUs) erzielt werden können. Unsere Ergebnisse zeigen, dass unsere Hardware-Implementierung auf einem Maxeler FPGA-System eine Implementierung in Software hinsichtlich der Datenverarbeitungsleistung übertreffen kann und gleichzeitig energieeffizienter ist. Zudem können wir belegen, wie instanzspezifische Designs sogar nach Bedarf *on-the-fly* generiert werden können, sodass die erzielte Beschleunigung die zusätzliche Zeit für die Erstellung des FPGA-Designs mittels Hardware-Synthese überwiegt.

# **Table of Contents**

| Ac | knov                             | vledge                                                                                          | ments                                                                                                                                                                                                                                          | v                                                 |

|----|----------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Ał | ostrac                           | t                                                                                               |                                                                                                                                                                                                                                                | vii                                               |

| Zu | Isami                            | nenfas                                                                                          | sung                                                                                                                                                                                                                                           | ix                                                |

| Та | ble o                            | f Conte                                                                                         | ents                                                                                                                                                                                                                                           | xi                                                |

| 1  | <b>Intro</b><br>1.1<br>1.2       |                                                                                                 | on<br>ibutions Overview                                                                                                                                                                                                                        | <b>1</b><br>1<br>2                                |

| 2  | Four<br>2.1<br>2.2<br>2.3        | Field-<br>Design<br>MaxC<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5                           | ns: Reconfigurable Computing Programmable Accelerators                                                                                                                                                                                         | <b>3</b><br>3<br>5<br>6<br>7<br>7<br>8<br>9<br>10 |

| 3  | Excu<br>3.1<br>3.2<br>3.3<br>3.4 | Introd<br>3.1.1<br>3.1.2<br>3.1.3<br>Mode<br>3.2.1<br>3.2.2<br>Advan<br>3.3.1<br>3.3.2<br>3.3.3 | to Cryptography and Information Security<br>luction to Side-Channel Attacks                                                                                                                                                                    |                                                   |

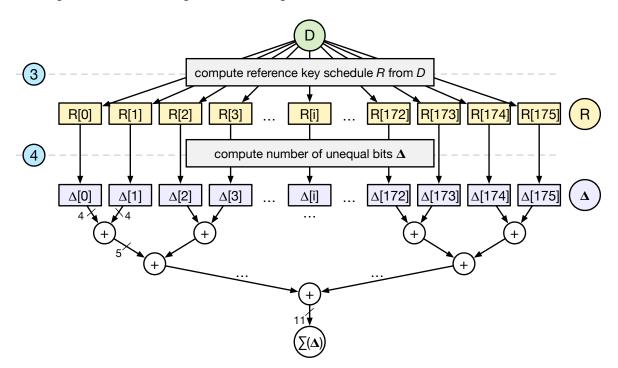

| 4  | <b>Inte</b><br>4.1<br>4.2        | Basic                                                                                           | Ite Findings: Identification of Secret Key Material         Idea and Software Approach         ware Implementation         Input         Heuristics         Computation of Reference Key Schedule         Computation of the Hamming Distances | 27<br>27<br>30<br>30<br>30<br>31<br>32            |

|   | 4.3  | Evaluation                                                 | 32 |

|---|------|------------------------------------------------------------|----|

|   |      | 4.3.1 Software Reference                                   | 32 |

|   |      | 4.3.2 Kernel Replication                                   | 33 |

|   |      | 4.3.3 Results                                              |    |

|   |      | 4.3.4 Discussion                                           |    |

|   | 4.4  | Chapter Conclusion                                         | 35 |

| 5 | Bra  | nch-and-Bound with Reconfigurable Hardware                 | 37 |

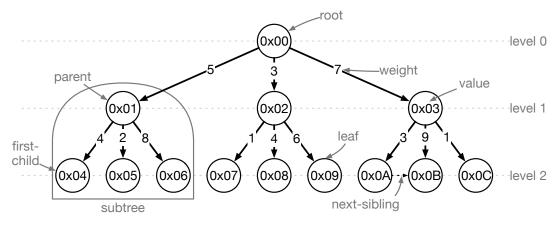

|   | 5.1  | Basics and Common Terminology                              | 38 |

|   |      | 5.1.1 Tree Data Structure                                  | 38 |

|   |      | 5.1.2 Traversal Strategies: Tree Structure and Search Path |    |

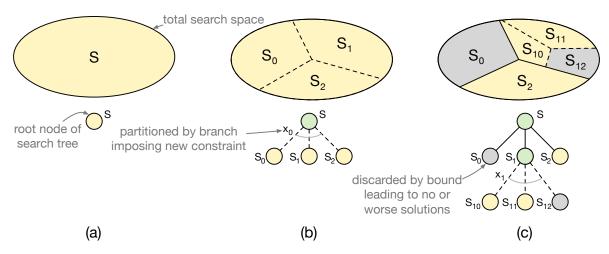

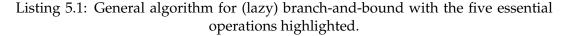

|   | 5.2  | Branch-and-Bound: General Idea                             | 40 |

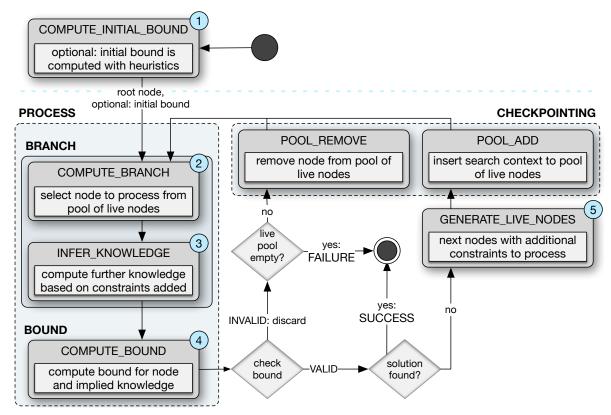

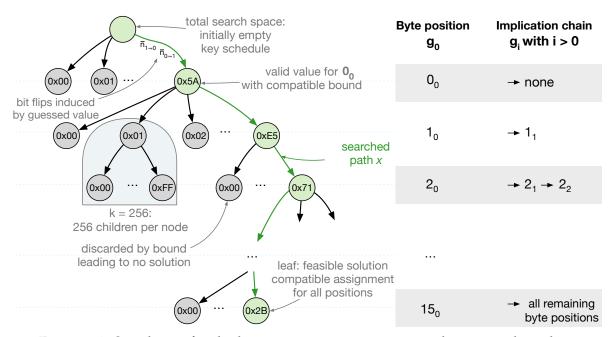

|   |      | 5.2.1 Algorithmic Pattern                                  | 41 |

|   |      | 5.2.2 State Machine Design for Reconfigurable Hardware     |    |

|   | 5.3  | Case Study: Secret Key Reconstruction                      | 45 |

|   |      | 5.3.1 Basic Idea                                           | 45 |

|   |      | 5.3.2 Software Approach                                    |    |

|   |      | 5.3.3 Bounding the Search Space: Error Model               |    |

|   | 5.4  | Branch-and-Bound in Hardware                               | 50 |

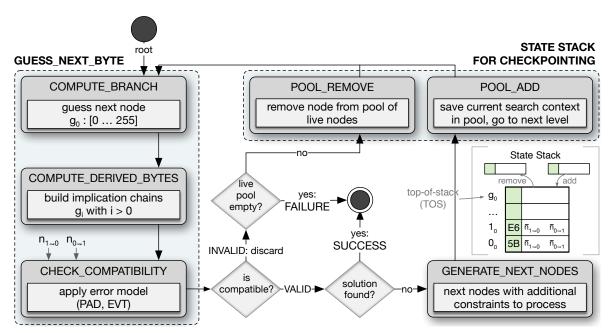

|   |      | 5.4.1 Software Translation: Concrete Finite State Machine  | 50 |

|   |      | 5.4.2 Selecting Branches                                   | 51 |

|   |      | 5.4.3 Computing Inferred Knowledge: Implication Chains     |    |

|   |      | 5.4.4 Checkpointing Tree Traversal                         | 52 |

|   |      | 5.4.5 Maintaining the Bound: Applying Error Model          | 53 |

|   | 5.5  | Evaluation                                                 | 55 |

|   |      | 5.5.1 Target Platforms                                     | 55 |

|   |      | 5.5.2 Error Metrics                                        | 56 |

|   |      | 5.5.3 Evaluation Scenario                                  |    |

|   |      | 5.5.4 Software Implementation                              | 57 |

|   |      | 5.5.5 Performance Comparison of Software to Hardware       |    |

|   | 5.6  | Chapter Conclusion                                         | 62 |

| 6 |      | k Stealing with Reconfigurable Hardware                    | 65 |

|   | 6.1  | Motivation and General Description                         |    |

|   | 6.2  | Extensions of the General State Machine                    |    |

|   |      | 6.2.1 Coordination and Synchronization of Stealing         |    |

|   |      | 6.2.2 Initialization and Termination                       |    |

|   | 6.3  | Evaluation                                                 |    |

|   |      | 6.3.1 Evaluation Scenario                                  |    |

|   |      | 6.3.2 Results                                              |    |

|   | 6.4  | Chapter Conclusion                                         | 74 |

| 7 | Inst | ance-Specific Computing with Reconfigurable Hardware       | 77 |

|   | 7.1  | Motivation and General Description                         |    |

|   |      | 7.1.1 Methods for Customization                            | 78 |

|   |      | 7.1.2 Generation of Instance-Specific Designs              | 79 |

|   | 7.2  | Instance-Specific Branch-and-Bound Search Trees            | 79 |

|   |      | 7.2.1 Instance-Specific Branching Order                    | 80 |

|   |      | 7.2.2 Generating Valid and Optimal Search Tree Structures  | 82 |

|   |      | 7.2.3 Selecting Instance-Specific Search Tree Structures   |    |

|   | 7.3  | Generation of Instance-Specific Hardware Designs           | 84 |

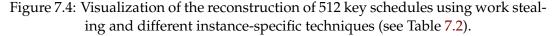

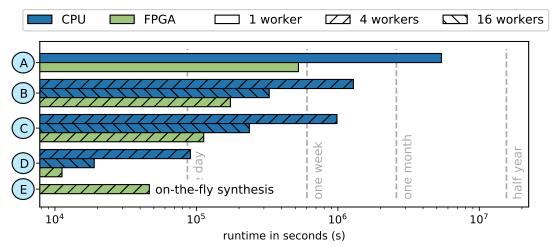

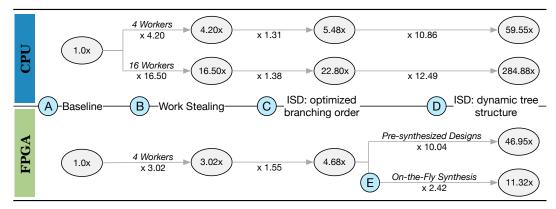

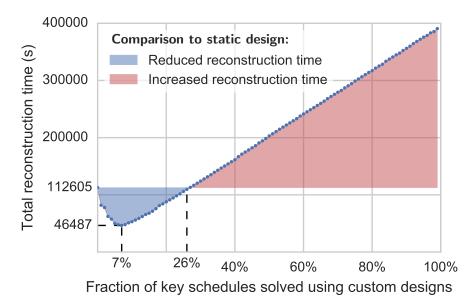

|                         | 7.4<br>7.5               | Evaluation7.4.1Results7.4.2On-the-Fly Hardware Synthesis7.4.3Discussion and Practical ConsiderationsChapter Conclusion | 85<br>87<br>88 |  |  |  |  |  |  |  |  |

|-------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|--|--|--|--|

| 8                       | Rela                     | ated Work                                                                                                              | 91             |  |  |  |  |  |  |  |  |

| 0                       | 8.1                      | Side-Channel and Cold-Boot Attacks                                                                                     |                |  |  |  |  |  |  |  |  |

|                         | 0.1                      | 8.1.1 Acquisition of Sensitive Data                                                                                    |                |  |  |  |  |  |  |  |  |

|                         |                          | 8.1.2 Search and Extraction of Secret Key Material                                                                     |                |  |  |  |  |  |  |  |  |

|                         |                          | 8.1.3 Reconstruction of Secret Keys                                                                                    |                |  |  |  |  |  |  |  |  |

|                         | 8.2                      | Branch-and-Bound in Soft- and Hardware                                                                                 |                |  |  |  |  |  |  |  |  |

|                         |                          | 8.2.1 Parallelization and Work Stealing                                                                                |                |  |  |  |  |  |  |  |  |

|                         |                          | 8.2.2 Instance-Specific Computing                                                                                      | 98             |  |  |  |  |  |  |  |  |

|                         | 8.3                      | Chapter Conclusion                                                                                                     | 99             |  |  |  |  |  |  |  |  |

| 9                       | <b>Con</b><br>9.1<br>9.2 | clusion<br>Summary                                                                                                     |                |  |  |  |  |  |  |  |  |

| Li                      | st of '                  | Tables                                                                                                                 | 104            |  |  |  |  |  |  |  |  |

| Li                      | st of                    | Listings                                                                                                               | 105            |  |  |  |  |  |  |  |  |

| Li                      | st of :                  | Figures                                                                                                                | 108            |  |  |  |  |  |  |  |  |

| A                       | Acronyms                 |                                                                                                                        |                |  |  |  |  |  |  |  |  |

| A Supplemental Material |                          |                                                                                                                        |                |  |  |  |  |  |  |  |  |

| A                       | uthor                    | 's Publications                                                                                                        | 116            |  |  |  |  |  |  |  |  |

| Bi                      | bliog                    | graphy                                                                                                                 | 118            |  |  |  |  |  |  |  |  |

### **Chapter 1**

## Introduction

The branch-and-bound (B&B) algorithmic pattern is a powerful tool for processing very large search spaces or to find optimal solutions in them. It is the most commonly used algorithmic pattern and systematic method to solve combinatorial optimization problems such as scheduling, logistics, applied mathematics, planning, decision processes and many others. Branch-and-bound algorithms explore tree-based search spaces systematically by eliminating unpromising subtrees as early as possible. Nevertheless, the exploration is highly time-intensive for large problem instances because the search trees are growing exponentially and are extremely irregular in size and structure. There are several techniques to tackle those instances. The most promising ones are parallelization and the utilization of problem-specific features.

#### 1.1 Contributions Overview

In this thesis, we systematically analyze and study the insufficiently understood efficient realization of branch-and-bound algorithms for field programmable gate arrays (FPGAs). FPGAs have proven to be highly efficient in terms of chip area, power consumption and performance with a high potential for specialization for different workloads. However, the irregular structure of branch-and-bound algorithms and the control-driven execution flow makes them not the typical class of problems that have been addressed with FPGAs. The main contributions of this thesis are:

- 1. We identify general elements that are required to implement B&B problems with FPGAs and abstract them as a finite state machine design. We present an architecture that uses highly optimized combinational datapaths for the performance-critical levels of the search tree and more resource-efficient pipe-lined ones for the less frequent and more complex levels. On the basis of a concrete case study, we show how a transformation from software to hardware alone can lead to improvements in orders of magnitude in performance by exploiting the architectural features and different levels of parallelism of FPGAs.

- 2. We then extend this design in order to allow multiple hardware workers to dynamically share and balance their load using work stealing when exploring the large search space of a branch-and-bound problem. We present a parallel FPGA architecture that is scalable with the available resources and provides speedups proportional to the number of workers.

- 3. Using the parallelized design, we further accelerate the execution by exploring the advantages of instance-specific computing on FPGAs. We present a fully automated tool flow to generate designs that are custom tailored to a specific problem instance that existing tools do not deliver. Our work shows that this technique is in particular beneficial to accelerate problem instances that are especially difficult and highly time-intensive to solve.

- 4. We evaluate all of our proposed methods and compare each result to those obtained using similar techniques in software on CPUs. In contrast to existing approaches, we also demonstrate how instance-specific designs can be generated on-the-fly such that the provided speedups outweigh the additional time required for a complete design synthesis.

All presented concepts and results have been peer-reviewed and published in two premier international conferences [3, 2] and one journal article [1]. Beside Heinrich Riebler as lead researcher, first author and main contributor, Robert Mittendorf contributed during his Master's thesis [207] to the first implementation of work stealing in soft- and hardware. Thomas Löcke contributed during his Master's thesis [186] to the first implementation of instance-specific computing in soft- and hardware and, finally, Michael Laß contributed as a student assistant to the evaluation results used in our journal article [1]. A complete list of the author's publications is summarized before the main bibliography starting on page 117.

#### **1.2 Thesis Structure**

The remainder of this thesis is structured as follows: Chapter 2 starts with the foundations on reconfigurable computing and the design flow and programming model for FPGAs that is used in the practical parts of this work. Chapter 3 takes an excursion to the cryptography and information security domain to motivate the case study used throughout the thesis to apply the concepts to real-world and relevant problems. In Chapter 4, we present our intermediate findings with regard to our case study. The tackled subproblem in this chapter is highly suitable for FPGAs and our presented solution significantly outperforms software-based implementations. The next three chapters present the original research on efficient branch-and-bound algorithms for reconfigurable hardware. In Chapter 5, we present the main concepts and building blocks for a general hardware design for processing large search trees using branch-and-bound with FPGAs. Afterwards, we describe in Chapter 6 the extension of our general, but sequential branch-and-bound hardware design to allow parallelization of the work on FPGAs using hardware workers. The resulting parallel design is then further improved by using instance-specific computing in Chapter 7. We describe how different search trees using B&B can be dynamically constructed by utilizing application- and instance-specific information to improve the search process including an on-the-fly hardware acceleration. Finally, we present related work in Chapter 8 and conclude our work and point to directions for future research in Chapter 9.

### Chapter 2

# Foundations: Reconfigurable Computing

This chapter provides the background information and foundations on reconfigurable computing that are used in the following chapters. The ideas and concepts in this thesis heavily rely on practical parts, implemented and evaluated on reconfigurable hardware, namely on field programmable gate arrays (FPGAs).

In this chapter, we first give a general motivation for reconfigurable computing in Section 2.1. We describe the ideas and building blocks of FPGAs and then outline the hardware acceleration with FPGAs. The hardware acceleration is first explained in Section 2.2 on a general level and then in Section 2.3 concretely on the components and program blocks of the MaxCompiler, which is the programming model used for the design and implementation of our concepts.

#### 2.1 Field-Programmable Accelerators

A computer system is typically considered from two perspectives, the software and the hardware side. In a traditional view, the hardware side offers a fixed functionality after fabrication and the software provides the flexibility by executing different applications to change the type of computation. Reconfigurable computing [129, 215] tries to blend both perspectives together by making the hardware (datapath, memory and/or functional units) programmable after fabrication. The configuration (usually of the size of several kilo- or megabytes) is loaded onto the reconfigurable hardware via a data stream of bits and can be partially or completely reassigned [89, 227]. Computer systems using reconfigurable hardware are reprogrammed to adapt their *architecture* to the requirements of the type of computation that is under execution. The ability to make substantial architectural changes can lead to orders of magnitude better implementations in terms of performance (execution time), utilization (chip area efficiency) and power usage [220, 163].

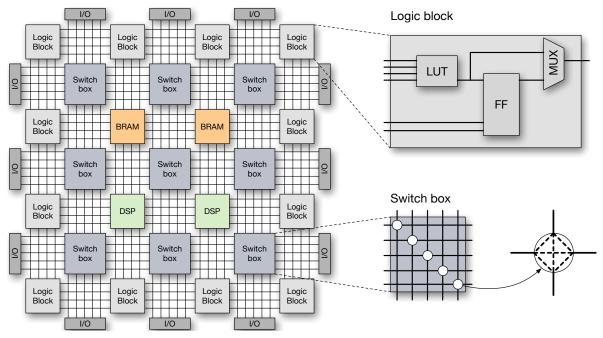

A field programmable gate array (FPGA) [274, 172] is the most prominent universally programmable reconfigurable hardware. The FPGA can be reconfigured in the field by the user after fabrication. The programming (also called configuration) determines the functionality of individual flexible logic blocks and their flexible interconnect (see Figure 2.1). The logic blocks are laid out as an array structure and can be grouped into hierarchical clusters, which are interconnected with configurable switch boxes. The three most important elements of a logic block are lookup tables (LUTs) to implement combinational logic, flip-flops (FFs) to implement sequential

logic to buffer values, and configurable multiplexers to select between these elements. The configuration to program the FPGA is generated by a logic synthesis. The process is similar to the compilation of software but needs hours to days to complete, because of the tremendous search space to place and route the desired functionality to the logic blocks. In fact, branch-and-bound search algorithms are often used for this process [260, 258, 104, 146].

The performance of an FPGA design depends on a number of assessable factors, such as the number of cycles required to perform a task and the read/write rate of the memory and communication buses. The functionality is fixed after configuration and the runtime of an application is given by the number of cycles and the achieved clock frequency. There are no dynamic events such as interrupts. This makes the performance of an FPGA design well predictable and allows the modeling of the expected acceleration before its actual implementation. It can help to verify the results of the design and implementation and to identify possible sources of bottlenecks.

Figure 2.1: Schematic illustration of an FPGA architecture. The array structure consists of logic blocks, switch boxes and specialized elements (DSPs or BRAMs).

Over time, modern FPGAs have expanded their building blocks beyond the basic logic capabilities mentioned above to include more specialized elements fixed in silicon. Conceptually, these elements can also be built from the basic logic primitives, but with higher chip area requirements and lower clock frequency. Examples of these building blocks include digital signal processor (DSP) blocks typically used for multiplications, multi-gigabit transceivers for high-speed communications, hard IP processor cores to mimic system-on-chip behavior and, most importantly, external and local (high bandwidth) memory. External memory is typically on-board DDR RAM. Local memory is embedded into the FPGA's array structure as BRAMs. A single BRAM can store several kBits and multiple BRAMs can be cascaded to form larger memory blocks with configurable address depths and data widths. The logic of lookup tables can also be used as local memory to store several bits. This type of local memory is called LUT RAM.

FPGAs are especially suitable for computationally intensive applications with a regular computation and/or communication pattern. Individual independent operations can be processed completely in parallel on spatially different computing units. The resulting execution is data- and not control-driven. Control-driven systems perform the required calculations at different points in time on the same computing units (temporal processing). The computing unit has to be able to perform a variety of functions and is therefore typically more general than necessary for a concrete task. In contrast, data-driven FPGA designs have their own custom computing unit for the respective calculation (spatial processing). Each custom unit can be exactly specialized for the required task. FPGAs have been used for many data-driven application domains, e.g. from image processing and recognition [21, 271, 108, 71], pattern matching in data or network streams [64, 26, 182, 181], or in the information security domain [285, 267, 231]. FPGAs also have very suitable properties in the cryptography domain [138, 79]. Cryptographic applications usually require a lot of computing power and can be strongly spatially parallelized due to their often independent (sub-)structures. Compared to CPUs, FPGA-accelerated implementations can achieve a much higher throughput and energy savings when encrypting and decrypting data and can still be flexibly configured to different parameters [282, 240, 261, 119].

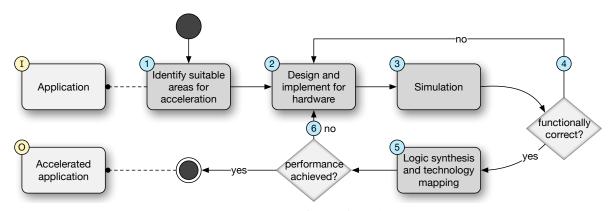

Figure 2.2: Schematic design flow of hardware acceleration.

#### 2.2 Design Flow of Hardware Acceleration

In Figure 2.2, we show a schematic sequence of how an application can be accelerated using FPGAs. At the beginning, an original application ① usually exists in software that should be accelerated in parts in hardware. In the software application, areas that are suitable for acceleration must be identified. This step ① is usually performed by profiling the application with representative data sets. Loops are typically good candidates for recurring tasks that can be offloaded. Once the affected areas have been identified, the developer transforms the computation into a form suitable for hardware in step ②. The developer can use components from the used programming model and programming language to implement the computationally intensive part in hardware. FPGAs work best when they can continuously perform the same operations in a parallel and pipelined fashion. The major part of the development only takes place on simulation level ③, because the actual hardware synthesis is very time consuming. The process needs to be iterated in ④ until the desired *functionality* is achieved. The simulation can only give hints on the correctness of the implementation. The actual performance and utilization of the resources in hardware can only be checked after the logic is synthesized in the step (5). If the design and implementation meet the desired functionality *and* performance, the accelerated application (0) is the outcome. Otherwise, the design needs to be adjusted and the steps (1–6) have to be repeated.

#### 2.3 MaxCompiler Programming Model

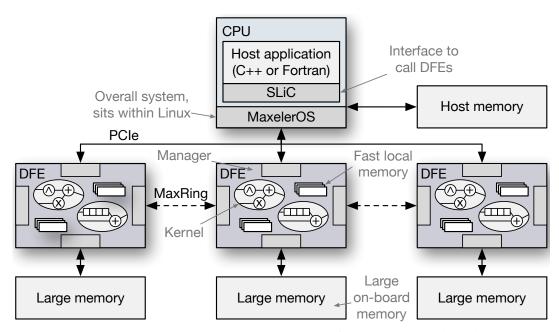

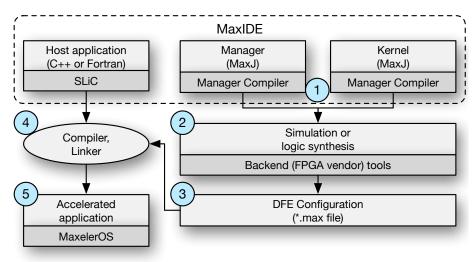

The design flow and implementation of the practical parts of this thesis are based on the MaxCompiler [222] programming model and tool chain. It is mainly driven by Java and offers predefined APIs for specifying the FPGA implementation as socalled data flow engines (DFEs). Each DFE is comprised of one or more kernels, which implement the application logic, and of a manager that controls the routing of data streams between kernels, the CPU and off-chip memory. Figure 2.3 outlines the different components and general architecture. The system can connect multiple FPGAs and memory devices via PCIe to the CPU where the host application is located. The computation and communication tasks are divided into kernels and managers. This separation of the application eases the design and implementation process.

Figure 2.3: Components and overall architecture of the MaxCompiler. The depicted system consists of three FPGA cards connected through PCIe, each with on-board memory.

The development of an accelerated application with the MaxCompiler typically consists of three program parts: a host application, the kernel and the manager. In this thesis, state machines (SMs) will also play an important role and are also explained. They can either be implemented in the kernel or the manager.

#### 2.3.1 Host Application

The host application can be written in C/C++ or Fortran. It calls functions to load the FPGA configuration and initializes the direct memory access (DMA) transactions. These are required for the actual data transfer to and from the FPGA. In addition, the host application allocates and initializes the data buffers and transfers them via the so-called simple live CPU (SLiC) interface. The raw data is loaded from the host to the FPGA via PCIe. As soon as enough data is available, the calculations start immediately on the FPGA. At the same time, available results are transferred back to the host application in parallel. The SLiC interface also provides functions to execute specific tasks on the DFE and set system parameters for the whole FPGA.

#### 2.3.2 Kernel

A kernel (written in MaxJ) contains the parts of the actual application logic and gets its input data from the manager. It can be seen as a unidirectional cycle-free graph, where the data streams from one side to the other. The kernel execution typically has a fixed number of cycles to complete, dependent on the size of the input stream. The kernel graph is usually divided into a control part implemented with counters and a data part. The graph consists of several node types, which are listed in Table 2.1.

- Calculation nodes perform arithmetic or logical operations (e.g. +, -, \*, <, & or  $\oplus$ ) or represent type conversions from one data type to another (e.g. floating-point number, fixed-point number or integer).

- Value nodes provide parameters. They are either constant or scalar. The host application can set scalar value nodes at runtime.

- Stream position nodes allow access to different positions in the data stream. They can either go forward or backward.

- Multiplexer nodes enable the integration of decisions.

- Counter nodes help the control flow of the application. They allow the reaction to certain positions in the data stream or can indicate boundary conditions such as the start or end of the stream.

- $\square$  I/O nodes connect the kernel externally to the manager. They serve as an interface for data input and output.

Table 2.1: Possible node types of a kernel graph.

A compiler converts a program to generate such a data flow graph. The structure of the data flow graph represents the logic of the application. The graph shows the nodes for the machine commands or executable actions and the edges for the dependencies of the data. The connections are fixed and no additional control instructions are required. As soon as the preconditions for an action are met, it is executed and the result is forwarded to the next action in the graph. Individual independent actions are processed completely in parallel on spatially different computing units. The resulting execution of the statements is therefore data-driven rather than control-driven. In the second step, optimizations and transformations take place in the graph. The actual code for the FPGA is then generated from the graph in a hardware description language.

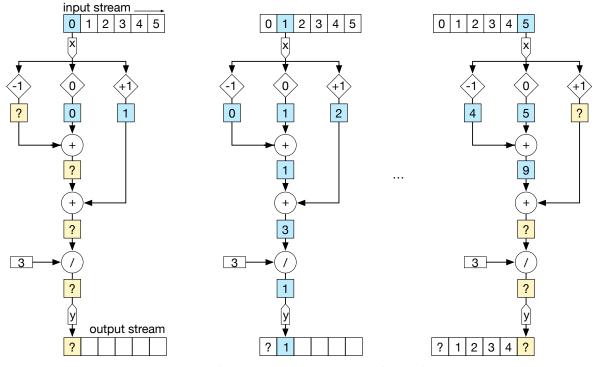

A simple example using these nodes is shown in Figure 2.4. It receives an input stream consisting of six elements and computes the moving average with a sample window of three elements. To do this, the current element is simply added to the previous and subsequent elements and divided by three. The left part of the figure shows the start phase with empty actions in the data flow (highlighted in yellow), because the first element has no predecessor. The middle part of the figure shows the first tick when the pipeline is completely filled and correct results are produced in every tick. The final phase on the right side has again empty action nodes, because the end of the stream is reached. The example shows the consistent and regular flow of data through the graph and the respective values. The example highlights that the common fork/join constructs from multi-core processors are no longer necessary because parallelism implicitly exists.

Figure 2.4: Example of three phases in the data flow of an application.

#### 2.3.3 Manager

The manager [188] typically instantiates itself and the kernels. Then both components are aligned to each other. For example, it organizes the concrete type and size of the input and output of data through a kernel. The data streams can also be configured to be routed to other FPGAs or to external memory. Figure 2.3 shows the connection between different FPGAs using the dedicated high-speed MaxRing interconnect. Each FPGA can have up to two direct, bidirectional MaxRing connections. A header file is generated from the configuration of the manager via the SLiC interface. This header file defines the signature of the data streams (e.g. the data types) and contains various actions for the host application, such as whether the call to the kernel should be synchronous or asynchronous. Other important aspects of the manager are the settings of the hardware level parameters. These are mainly the parameters to guide the hardware synthesis process (target frequency, seed, level of effort to place and route, etc.). The settings not only help to improve performance, but also can determine the success of the hardware synthesis.

#### 2.3.4 State Machines

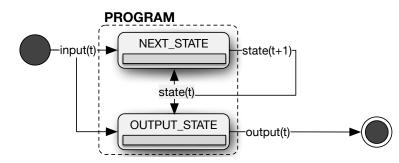

Most importantly for this thesis, the MaxCompiler offers also an API [189] to describe finite state machines (FSMs) that can control memory streams and datapaths for applications that can not be expressed as a simple streaming datapath such as regular kernels. FSMs and state machines (SMs) allow the implementation of fine-tuned control blocks in the kernel and manager. They provide deeper control mechanisms for the data flow with better accessibility than a kernel with counters alone. Figure 2.5 illustrates the execution model and the connection between the inputs and outputs when using state machines. Two functions describe the behavior in each cycle: NEXT\_STATE and OUTPUT\_STATE. Starting from the current state in cycle *t* and the current input, the first function calculates the next state for cycle (t + 1). The second function controls the output of the machine depending on the current state and the input. Both functions are executed completely in parallel. The state machine stores the data of the current cycle for the next cycle.

Figure 2.5: Execution model for state machine transitions.

The MaxCompiler offers state machines in two different variants: embedded in the kernel as a kernel SM or directly integrated in the manager as a manager SM. Both variants follow the execution model described above in the illustration but differ in two decisive aspects:

First of all, a kernel state machine still strictly follows the data flow model described above for kernels and only uses the state machine APIs to simplify a complex control block. The state machine embedded in a kernel is executed in every tick completely aligned to the surrounding kernel. It usually receives an input in every tick and produces an output in every tick. Consequently, kernel scheduling directly determines state machine scheduling.

In contrast, the developer can use a manager state machine if the regular data flow model does not fit the application. The manager state machine does not necessarily process an input in every tick and generate an output in every tick. The manager state machine is executed at every system clock and has no surrounding kernel. Hence, a manager state machine does not have a fixed number of cycles to complete, but is rather signal driven. Its scheduling is typically directly linked to the production of an output, the result. The connection to the input or output is controlled by the state machine itself via signals with requests and responses. The developer has to manually take care of the communication control. In particular, the state machine needs to signal when new data should be read and when valid data is present at the output. An essential part of the design and implementation in this thesis is based on manager state machines.

#### 2.3.5 Compilation Tool Flow

Finally, the MaxCompiler offers a supporting tool for the development of the described components, the MaxIDE. The interaction of the components and the compilation flow is shown in Figure 2.6. The kernel and manager compilers (1) translate the respective programs (written in MaxJ, an extended form of Java) into machine language. In the first step, the normal Java compilation with syntax checking takes place. The generated .class-files are then executed. The execution includes three intermediate steps: the construction of the data flow graph, the optimization and transformation of the graph, and the generation of the configuration for the FPGA by backend (FPGA vendor) tools (2). The MaxCompiler is able to take care of type conversions and can automatically perform optimizations such as retiming [173], buffer size optimization and pipelining. The execution of these three steps produces a .max-file (3) that can either be simulated or completely synthesized in hardware. The .max-file contains the configuration of the FPGA as a bitstream and further data that the FPGA needs to control the data transfers. Finally, the host application is compiled, merged with the .max-file and linked against the required libraries (4). The resulting binary file (5) can be invoked standalone and the MaxelerOS serves as a bridge between software and hardware, similar to a regular hardware driver.

Figure 2.6: Compilation tool flow.

#### 2.4 Chapter Conclusion

In this chapter, we provided background information and foundations on reconfigurable computing required for this thesis. The ideas and concepts introduced in the following chapters heavily rely on practical parts and are designed and implemented for FPGAs. We outlined the architecture and building blocks of FPGAs and introduced the MaxCompiler as the main programming model that is used for the actual implementation.

### **Chapter 3**

# **Excursion to Cryptography and Information Security**

In this chapter, we will take an excursion to the cryptography and information security domain. The overall ideas for studying general branch-and-bound (B&B) on FPGAs started with the examination of very uncommon problems for FPGAs, namely the so-called cold-boot attacks (CBAs). Cold-boot attacks are part of sidechannel attacks against computer systems that rather exploit specific aspects of the whole ecosystem where algorithms are implemented and executed, instead of exploiting an algorithm itself. Side-channel attacks form a very interesting and important area in the information security domain. We analyzed and studied cold-boot attacks for FPGAs and designed and developed very efficient implementations. From the analysis and implementations we were able to generalize the solution to be able to transfer the lessons learned to other branch-and-bound problems outside the specific domain. With this background information in mind, the following structure of this thesis might be easier to assess.

In this chapter, we will give a general motivation and background information required to understand the challenges imposed by our case study. In Section 3.1, we give an introduction to general side-channel attacks and the specialties of coldboot attacks. We work out three typical phases that are required to spawn a real attack vector. Then, in Section 3.2, we present two distinct error models that are required by the branch-and-bound algorithm used in this thesis to be able to prune the search space. Finally, we describe the functionality of the advanced encryption standard (AES) in Section 3.3 because our case study makes heavy use of its internal operations.

#### 3.1 Introduction to Side-Channel Attacks

According to a study by the Ponemon Institute [225], 12,000 laptops are lost at US airports per week. The study states that about 53% of business travelers carry sensitive data. In a later study [226] of the same institute, 275 organizations in Europe were interviewed. The researchers found that about 8% of all laptops in companies are lost during their lifetime. During the twelve-month study period, about 72,000 laptops disappeared. The Ponemon Institute estimates the cost per laptop at about  $35,000 \in$ . Only a small fraction of this sum is made up of hardware costs. The loss of availability, integrity and, most importantly, confidentiality of information represents the far larger cost share. Even though some definitions and numbers presented by the studies are controversial [32, 217], the overall risk and consequences associated with lost laptops should raise awareness. A recent survey [165] indicates

that most companies have unprotected data and poor information security practices, making them vulnerable to attackers. The consequences of such incidents for a company can include significant financial and customer confidence losses.

The users of modern communication and information systems therefore demand security technologies against the threats of unintentionally loosing or leaking any kind of data. Cryptography and information security techniques offer the key technologies for effectively counteracting threats of integrity and confidentiality. Companies and individuals increasingly encrypt the data stored on hard disk drives by using full disk encryption tools and the data transferred during communication by using secure protocols (for example, HTTPS [235], VPN [62] or WPA2 [170]).

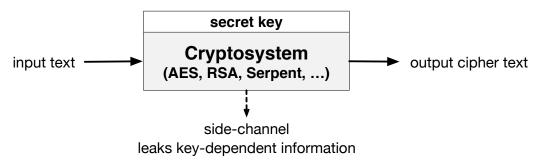

The tools and protocols support different ciphers (for example, AES [12], RSA [237], ECC [151], Serpent [18], or Twofish [243]) in different combinations, configurations and modes. While modern cipher algorithms themself are considered secure, actual implementations have to keep the secret key material in main memory. For efficiency reasons, auxiliary key material is stored in addition to the secret key itself. The key material is derived from the secret key itself and can contain round keys in the case of symmetric ciphers such as AES/Serpent/Twofish or cofactors/modulus in the case of public-key cryptosystems such as ECC/RSA. This additional material is always needed in the encryption and decryption process. It is very sensitive, because it can reveal characteristics of the secret key itself. Keeping the sensitive key material in the main memory of a computer system for efficiency reasons was assumed to be secure. Firstly, the main memory was expected to be volatile and quickly change into a default state erasing its contents when removing the power supply. And secondly, memory cells were expected to be isolated, not interfering each other states allowing privilege separation between different processes.

In recent years, both assumptions have been invalidated by security experts. In the first case, Skorobogatov [255] and Halderman et al. [126] have shown that the memory contents of SRAM and DRAM decay surprisingly slowly over time. The decay can be slowed further by cooling the chips, which opens the possibility to attack the secret keys and thus to circumvent the cryptography and information security procedures. In the second case, Kim et al. [149] first were able to bypass the isolation between memory cells to alter values in order to violate the systems integrity and later Kwong et al. [164] exploit the same *row hammering* technique to also read the memory contents from this side-channel affecting the system's confidentiality.

In the following, we will mainly focus on specific details imposed by cold-boot attacks. The basic ideas, attack vectors and algorithmic challenges are very similar to other side-channel attacks.

#### 3.1.1 Cold-Boot Attacks

The cold-boot attack (CBA) is a serious problem for software-based encryption programs. By observing, measuring and combining certain properties, such as patterns in the main memory, the attacker attempts to draw conclusions about parts of the secret key material in the main memory. The cold-boot attack exploits especially the long decay time of memory cells, also called the remanence effect [141].

#### 3.1.2 Remanence Effect of Main Memory

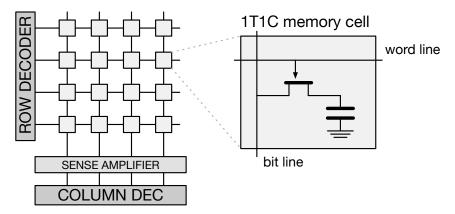

In modern computer systems, at runtime the main memory typically contains the programs to be executed accompanying the corresponding data – also known as the von Neumann architecture [276]. The main memory module is an electronic circuit consisting of a large number of cells, whereby each cell essentially encodes a single bit of data. Figure 3.1 shows the most commonly used variant of a single dynamic random access memory (DRAM) cell realized as a one-transistor one-capacitor (1T1C) pair. Conceptually, the capacitor holds a charge to store a binary value (high charge for logic 1 and low for logic 0) and the transistor acts as a controller enabling reads and writes to retrieve and change the value.

Figure 3.1: Schematic illustration of the memory chip organization realized with one-transistor one-capacitor (1T1C) DRAM memory cells.

The memory cells implemented as static random access memory (SRAM) retain its data while the power supply remains. In contrast, DRAM cells are volatile, which means that the charge in the capacitor will slowly leak away. Depending on the memory chip organization, the cell is hard-wired to either power or ground leading to a decay of the cell to either logic 0 or 1 – the so-called *ground state*. To prevent the cell from losing its stored value and returning to its ground state, it must be refreshed periodically with current. As a result, a DRAM main memory module has a defined maximum refresh interval before the cells start to return to their ground state. As bit errors in the main memory have serious consequences for the program execution and for the stability of an entire system, the manufacturers of DRAM use very short refresh intervals (in the range of 64 milliseconds or less) to keep the probability of unwanted memory decay extremely low. In fact, modern memory cells are even refreshed after read operations to prevent the destruction of data, due to the very cost-efficient nature of the design.

When a system is turned off or the main memory module is suddenly removed, the DRAM cells are not refreshed anymore and the stored data is lost. However, it has been shown by Halderman et al. [126] that the memory cell contents are not lost immediately. The decay can be slow enough to allow (partially) retrieving its contents, especially at low temperatures by artificially cooling the memory chip. This remanence effect is primarily attributed to the high density of memory cells and opens an attack vector on cryptographic applications that keep secret keys in DRAM for encryption and decryption of data.

Figure 3.2: Main phases of a cold-boot attack.

#### 3.1.3 Attack Vector and Relevance

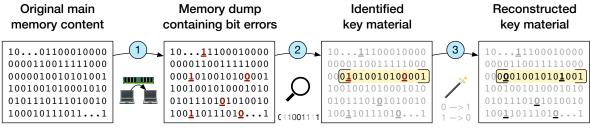

In a cold-boot attack [47, 16, 218, 211, 250], physical access to the target system by the attacker is a prerequisite. The attacker can get temporary access to the victim's computer (e.g. in the office during lunch break) or steal the victim's laptop at an inattentive or hectic moment. Another prerequisite is that the computer is in an active state (screen lock, standby, hibernate, etc.) at the time of the attack. The victim must have booted up the computer and logged in. Otherwise, the main memory contains no secret key material. The attack vector is depicted in Figure 3.2 and can be divided into three successive phases for better structuring [275]:

- 1 Acquisition of the main memory contents.

- 2 Search and extraction of the secret key material.

- 3 Analysis and reconstruction of the secret key.

The attacker's goal is thus to read the contents of the main memory, to find all the key material in it, and then to find and reconstruct the secret key. In the case of a successful attack, the attacker is able to decrypt the secret data or undermine the secured communication channel.

(1) Acquisition of the Main Memory Contents The acquisition of the memory content does not require any special hardware or software. Depending on how much time and resources the attacker has at her control and how many countermeasures are expected to be taken by the victim's system, the attacker can choose and adjust a suitable method presented by Halderman et al. [126]. The attacker typically obtains an image of the main memory contents by either rebooting the machine from a USB drive that dumps the contents to a persistent storage, or by physically transplanting the memory modules into another machine that is under the attacker's control. If the reboot process or the transplantation is done quickly, only a small fraction of the bits will have changed their value due to memory decay. The main memory can be strongly cooled during this process, which reduces the expected number of decayed errors. But as this procedure cuts the power to the memory module, the stored contents often contain bit errors. As individual bits can change their stored value, the acquisition of the memory content does not provide an exact copy. We call the proportion of decayed to total bits the *error rate*. The error rate is highly dependent on the type of the side-channel attack. For cold-boot attacks, the error rate is directly related to the moment of the last refresh of the memory. The longer the memory is not refreshed, the more bits decay. The result of a decay due to a missing refresh is a bit error in the corresponding cell of the memory. Details on the specific behavior and distribution of the decay over time are presented by Halderman et al. [126].

(2) Search and Extraction of the Secret Key Material In the next step, secret key material–in essence, (pseudo) random numbers of 128, 192 or 256 bits length–has to be identified in the memory dump with the typical size of several gigabytes (*key search*).

The secret keys alone are very small and contain a high entropy, which is difficult to search for. However, since the actual encryption and decryption operations require not just the secret key, but also auxiliary key material (for example, round keys), the key material is usually pre-computed and stored as a contiguous block in main memory. By exploiting the publicly known cryptographic structure of a cipher and layout of the key material in memory, the resulting memory image can be searched for sections that could correspond to (decayed) cryptographic keys.

③ Analysis and Reconstruction of the Secret Key Finally, the same information about the cipher can be used to correct bit errors in the extracted key material (*key fix*). The key material might contain many redundancies compared to the searched key, because it is derived from it. In this step, the redundancies can be used to detect and correct bit errors imposed by memory decay. If successful, the secret keys can be recovered and the cryptography and information security procedures can be circumvented.

Please note that especially the first two phases might slightly differ for other side-channel attacks, but follow exactly the same principles. For example, the most recent RAMBleed [164] attack uses a specific sequence of main memory accesses to cause bit errors in other locations of the memory than the one accessed. Leveraging those induced bit flips allows the attacker to read portions of the secret keys. This attack can even be performed remotely. The obtained secret keys have also bit flips similar to the decayed values for cold-boot attacks and therefore require same the reconstruction techniques as discussed in phase (3).

In the next section, we show how resulting bit errors caused by the side-channel attack can be modeled. Bit errors typically follow patterns and other dependencies that can be used in the search and the reconstruction processes to prune the search space and recover the secret key. We present two distinct models for bit errors caused by memory decay during cold-boot attacks.

#### **3.2 Modeling Bit Errors**

As mentioned earlier in Section 3.1.2, DRAM contents will gradually decay when the memory module is not refreshed. Halderman et al. [126] have investigated the main memory decay using different DRAMs (architectures, manufacturers, models, etc.) and test scenarios (with/without cooling, refresh at different time intervals, etc.) and

found some interesting decay patterns. Two of the most important findings can be summarized as follows:

- 1. Most bits decay continuously into the ground state of the main memory cell. The probability of this observation increases the longer the main memory is not refreshed. With a sufficiently long period without refreshing the cells, the entire memory cells decays to the ground state.

- 2. Only a very small fraction of bits (about 0.1%) flips in the opposite direction of the ground state. Wang [281] found for other DRAMs a slightly higher fraction of opposite bit flips, but confirms the overall observation.

The decay of memory is extremely asymmetric: this means that bit flips from 0 to 1 (denoted as  $0 \rightsquigarrow 1$ ) and bit flips from 1 to 0 (denoted as  $1 \rightsquigarrow 0$ ) occur with different probabilities depending on the ground state of the memory cells. Consequently, the number of errors is dominated by the decay of the bits into the ground state (with about 99.9%), compared to the rare decay in the opposite direction (remaining 0.1%). Hence, Halderman et al. proposed to completely ignore the unlikely flip direction opposite the ground state of the memory cell and assume only bit errors in the dominant direction. The model following this observation is called perfect asymmetric decay.

#### 3.2.1 Perfect Asymmetric Decay

Perfect asymmetric decay (PAD) assumes that only the dominant decay into the ground state of the cell exists and neglects the other 0.1% of the bit errors that can occur in real scenarios. This assumption offers very elegant and efficient implications in the search and recovery of secret keys. The most important implication is the *known bit*.

**Lemma 3.1 (Known Bit)** Under the assumption of perfect asymmetric decay, only bit flips in the direction of the ground state of the cell *M* exist. Consequently, all bits with the opposite value of the ground state are considered correct and can be directly determined. Equation 3.1 represents the relationship between the ground state and the known bit.

$$KNOWN\_BIT = \begin{cases} 1, \text{ if ground state of memory cell } M = 0 \\ 0, \text{ if ground state of memory cell } M = 1 \end{cases}$$

(3.1)

If, for example,  $d = 0x94 = 148_{10} = 10010100_2^1$  is the obtained decayed byte and  $M = 00000000_2$  is the ground state of the considered cell. Then every bit with the value 1 (here  $10010100_2$ ) is considered correct (or *known*) because a decay from  $0 \rightarrow 1$  cannot take place in the PAD model. Consequently, all divergent bit values ( $\neq 1$ ) at these positions can be immediately excluded (or bounded) in the recovery process of the secret key, because they are not compatible to the model.

The above considerations show that PAD provides a very simple way to determine the set of compatible candidates at an early stage. The next lemma shows how a candidate (a possible correct part of the secret key) can be checked.

<sup>&</sup>lt;sup>1</sup>Throughout the thesis, we will use numbers to different base systems. The general format is  $number_{base}$ . If the base is omitted, the decimal system (base 10) is used. Numbers with the prefix 0x or in monospace font are hexadecimal (base 16).

**Lemma 3.2 (Compatibility of Bytes with PAD)** If *c* is a candidate byte, *d* the decayed byte and *M* the ground state, then *c* and *d* are considered compatible if the following equation is holds:

is\_compatible<sub>PAD</sub>(c, d, M) = ( $c \oplus d$ )  $\land$  ( $d \oplus M$ ) = 0

For example, the candidate byte  $c = 11101011_2$  cannot decay to an observed byte  $d = 11010011_2$  when  $M = 00000000_2$  is the ground state, because the fourth bit must have flipped from 0 to 1:

is\_compatible<sub>PAD</sub> (

$$c = 1110\,1011$$

,  $d = 1101\,0011$ ,  $M = 0000\,0000$ ) (3.2)

= (1110 $1011 \oplus 1101\,0011$ )  $\land$  (1101 $0011 \oplus 0000\,0000$ ) = 0001 $0000 \neq 0$

On the other hand,  $c = 1110\,0011_2$  and  $d = 1100\,0000_2$  with *M* unchanged are compatible:

$$\texttt{is_compatible}_{PAD}(c = 1110\ 0011, \ d = 1100\ 0000, \ M = 0000\ 0000)$$

$$= (1110\ 0011 \oplus 1100\ 0000) \land (1100\ 0000 \oplus 0000\ 0000) = 0$$

The following, very important observation should be made clear by the formula and the examples: the compatibility between two bytes is decided in this model completely independent of past or following decayed bytes. It is a decision based on *local* knowledge (*d* and *M*), can be evaluated using simple operations and is therefore very suitable for hardware.

However, the PAD model fails for certain problem instances because in reality bit errors in both directions are possible. The next model includes this observation and is called *expected value as threshold*.

#### 3.2.2 Expected Value as Threshold

In our previous work [2], we proposed a threshold-based error model that takes both error directions into account and generalizes Halderman's observations. Our expected value as threshold (EVT) model separates the overall error rate of bit flips r (see Section 3.1.3) into bit flips in each direction  $1 \rightarrow 0$  (denoted as  $r_{1\rightarrow0}$ ) and  $0 \rightarrow 1$ (denoted as  $r_{0\rightarrow1}$ ):

$$r = r_{1 \leadsto 0} + r_{0 \leadsto 1}$$

The perfect asymmetric decay (PAD) model is subsumed in this model when  $r_{1 \rightarrow 0} = 0$  or  $r_{0 \rightarrow 1} = 0$ : i.e. reducing to a decay in only one direction. With given  $r_{1 \rightarrow 0}$  and  $r_{0 \rightarrow 1}$  rates, we can compute the expected number of bit flips in each direction, denoted as  $n_{1 \rightarrow 0}$  and  $n_{0 \rightarrow 1}$ , by multiplying the rates with the total number of bits *N* in the full key material:

$$n_{1 \to 0} = r_{1 \to 0} \cdot N$$

$$n_{0 \to 1} = r_{0 \to 1} \cdot N$$

Using this information, the next lemma shows how a candidate can be checked with the EVT model to estimate if the candidate is a possibly correct part of the secret key:

**Lemma 3.3 (Compatibility of Bytes with EVT)** We compute the number of bits that would have flipped from 1 to 0 and from 0 to 1 for a candidate byte *c*, denoted by  $c_{1 \rightarrow 0}$  and  $c_{0 \rightarrow 1}$ , and compare them against the number of expected bit errors *for the entire key material*. If one of the numbers exceeds its expected value, the candidate is not compatible, as outlined in Listing 3.1.

```

1 # Initialization with given r_{1 \leftrightarrow 0}, r_{0 \rightarrow 1} and N.

2 n_{1 \rightarrow 0} \leftarrow r_{1 \rightarrow 0} \cdot N

3 n_{0 \rightarrow 1} \leftarrow r_{0 \rightarrow 1} \cdot N

4 # Global information storing the already consumed bit flips.

5 \bar{n}_{1 \rightarrow 0} \leftarrow 0

6 \bar{n}_{0 \rightarrow 1} \leftarrow 0

7

8 is_compatible<sub>EVT</sub>(c, d, M) :

9

c_{1 \leftrightarrow 0} \leftarrow \text{ compute_bit flips_1_to_0}(c, d, M)

10

c_{0 \rightarrow 1} \leftarrow \text{compute_bit flips_0_to_1}(c, d, M)

11

# Check if bit flips induced by candidate exceed expected numbers.

12

13

if ( (c_{1 \rightarrow 0} + \bar{n}_{1 \rightarrow 0} \le n_{1 \rightarrow 0}) \land (c_{0 \rightarrow 1} + \bar{n}_{0 \rightarrow 1} \le n_{0 \rightarrow 1}) )

14

# Candidate is compatible. Update consumed bits.

15

\bar{n}_{1 \rightarrow 0} \leftarrow c_{1 \rightarrow 0} + \bar{n}_{1 \rightarrow 0}

16

\bar{n}_{0 \rightarrow 1} \leftarrow c_{0 \rightarrow 1} + \bar{n}_{0 \rightarrow 1}

17

return true

18

else :

19

return false

```

Listing 3.1: Compatibility check with the EVT error model.

Compared to the PAD model, the compatibility can no longer be decided locally between the decayed byte and the ground state. The bit errors from past and following bytes have an effect on each other and must always be carried throughout each compatibility check. This approach therefore requires *global* knowledge for the decision of the compatibility and has a high computational intensity compared to the PAD model, as will be shown later.

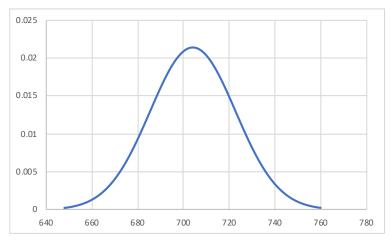

We also give an example for the compatibility check with the EVT model to create a better intuition. We assume the following scenario: The overall error rate is given by r = 5% with a ground state M = 0. Separating the error rate into the individual asymmetric direction of bit flips gives  $r_{1 \rightarrow 0} = 4.9\%$  and  $r_{0 \rightarrow 1} = 0.1\%$ . To compute the expected number of bit flips, we multiply the individual rates with the total number of bits in the full key schedule (N = 1408 for AES-128), which gives us  $n_{1 \rightarrow 0} \approx 69$ and  $r_{0 \rightarrow 1} \approx 1$ . This means that candidate bytes are compatible as long as any of these numbers is not exhausted. This is especially critical for  $r_{0 \rightarrow 1}$ , where only one bit flip opposite the ground state will be tolerated.

We recall the candidate byte from Equation 3.2. In the PAD error model the candidate  $c = 11101011_2$  cannot decay to the observed byte  $d = 11010011_2$ , because the fourth bit (underlined) must have flipped against the ground state from 0 to 1. However, with the EVT this candidate is compatible, as shown in the compatibility check in Listing 3.2.

The expected value as threshold model considers bit errors in both directions and is therefore the better model for practical considerations. However, it has some important differences to note. On the one hand, it is very difficult to determine the required thresholds (error rates in each flip direction) correctly. Due to the sensitivity

```

1 # Initialization expected number of errors:

2 \quad \text{\#} \qquad r = r_{1 \leadsto 0} + r_{0 \leadsto 1} = 0.049 + 0.001 = 0.05 \ \text{and} \ N = 1408 \,.

3 n_{1 \leadsto 0} \leftarrow 69 # = 0.049 \cdot 1408

4 \quad n_{0 \leadsto 1} \gets 1 \quad \text{ \# } = 0.001 \cdot 1408

5 # So far, no bit flips have been consumed.

6 \bar{n}_{1 \rightarrow 0} \leftarrow 0

7

\bar{n}_{0 \rightarrow 1} \leftarrow 0

8

9

# Compatibility check of first candidate.

10 is_compatible_EVT (c = 1110\,0011, d = 1101\,0011, M = 0000\,0000)

11 # Returns true, candidate is compatible.

12 # Candidate deviates at three bits.

13 # Number of consumed bits is updated.

14 \bar{n}_{1 \leadsto 0} \leftarrow 2 # 67 more bits can flip in this direction.

15 \bar{n}_{0 \leadsto 1} \leftarrow 1 # No more bit flips in this direction will be tolerated.

```

Listing 3.2: Compatibility check with the EVT error model applied to example.

of the model, the thresholds must be as accurate as possible, because invalid candidates pass the compatibility check if the threshold is too high and valid candidates do not pass the bound if the threshold is too low. From a statistical point of view, the search should not be bounded when the number of bit flips exceeds the expected number of bit flips, but instead when exceeding a certain number of errors that is unlikely to occur based on the given expected values. For simplicity, we assume that this deviation is already considered in the given error rates.

In this thesis, we will focus on the search and reconstruction of advanced encryption standard (AES) keys. Therefore, we describe the required functionality of AES in the next section, explain the basic cryptographic principles behind the individual operations and indicate the requirements for an implementation in hardware.

### 3.3 Advanced Encryption Standard

The advanced encryption standard (AES) [72] is one of the most used encryption algorithms and the default block cipher in a variety of systems and tools, e.g. disk encryption [103], WLAN, HTTPS, SSH [288] and VoIP [114]. AES is the successor of the data encryption standard (DES) [78, 66]. From 1976, DES has been the official encryption standard of the US government for over 20 years. To stop the increasing successful attacks against DES and to increase the key length of effectively only 56 bits, DES was executed three times in a row with three different keys (called Triple-DES or 3DES [251]). This temporary solution worked for that time, but was much slower. As a result, in 1997 a call for proposals for a successor of DES took place and yielded the algorithm Rijndael by Joan Daemen and Vincent Rijmen as the winner against 14 competing algorithms. Other finalists from the selection process are also known and used ciphers, for example, Twofish [243] or Serpent [18]. AES is a symmetric block cipher, has a fixed block size of 128 bits and features a variable key length of 128, 192 or 256 bits (each referred to as variant AES-128, AES-192 or AES-256).

#### 3.3.1 Key Schedule: Secret Key and Round Keys

The AES algorithm requires a set of round keys to encrypt and decrypt data. The way in which these are generated is decisive for the security of the cryptographic

process and defined by the AES key expansion function [72]. The secret master key is used as the first round key from which all other round keys are derived. The so-called *key schedule* is comprised of the master key and the (key size dependent) number of other round keys. The key schedule is the secret key material that is the target for side-channel attacks. The number of rounds varies and depends on the key length. Table 3.1 shows the common key sizes l with the number of rounds r.

| <b>number of round keys</b> r | key size <i>l</i> in bytes (bits) | key schedule in bytes (bits) |

|-------------------------------|-----------------------------------|------------------------------|

| 10                            | 16 (128)                          | 176 (1,408)                  |

| 12                            | 24 (192)                          | 312 (2,496)                  |

| 14                            | 32 (256)                          | 480 (3,840)                  |

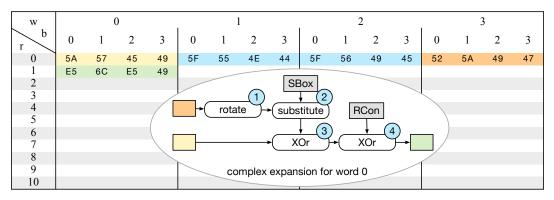

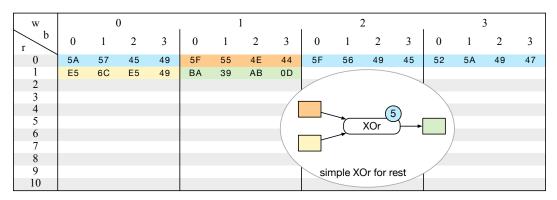

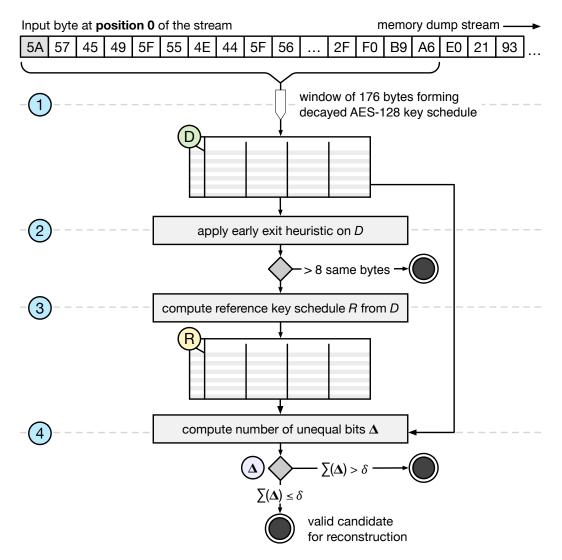

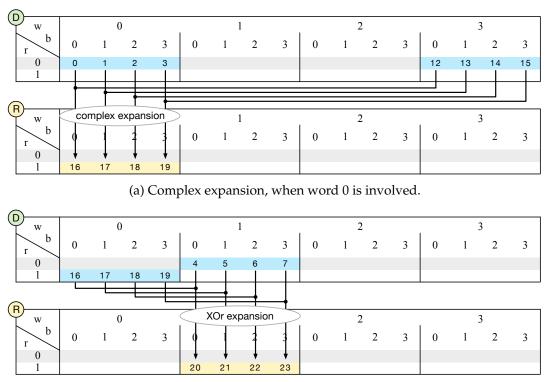

| w   |     | (   | )   |     | 1   |     |     |     | 2   |     |     |     | 3   |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| r b | 0   | 1   | 2   | 3   | 0   | 1   | 2   | 3   | 0   | 1   | 2   | 3   | 0   | 1   | 2   | 3   |

| 0   | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  |

| 1   | 16  | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  | 31  |

| 2   | 32  | 33  | 34  | 35  | 36  | 37  | 38  | 39  | 40  | 41  | 42  | 43  | 44  | 45  | 46  | 47  |

| 3   | 48  | 49  | 50  | 51  | 52  | 53  | 54  | 55  | 56  | 57  | 58  | 59  | 60  | 61  | 62  | 63  |

| 4   | 64  | 65  | 66  | 67  | 68  | 69  | 70  | 71  | 72  | 73  | 74  | 75  | 76  | 77  | 78  | 79  |

| 5   | 80  | 81  | 82  | 83  | 84  | 85  | 86  | 87  | 88  | 89  | 90  | 91  | 92  | 93  | 94  | 95  |

| 6   | 96  | 97  | 98  | 99  | 100 | 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 | 109 | 110 | 111 |

| 7   | 112 | 113 | 114 | 115 | 116 | 117 | 118 | 119 | 120 | 121 | 122 | 123 | 124 | 125 | 126 | 127 |

| 8   | 128 | 129 | 130 | 131 | 132 | 133 | 134 | 135 | 136 | 137 | 138 | 139 | 140 | 141 | 142 | 143 |

| 9   | 144 | 145 | 146 | 147 | 148 | 149 | 150 | 151 | 152 | 153 | 154 | 155 | 156 | 157 | 158 | 159 |

| 10  | 160 | 161 | 162 | 163 | 164 | 165 | 166 | 167 | 168 | 169 | 170 | 171 | 172 | 173 | 174 | 175 |

Table 3.1: Number of rounds *r* for key size *l*.

Table 3.2: Overall structure of an AES-128 key schedule *KS* and illustration of the ascending addressing scheme.

**Notation and Addressing Scheme** Table 3.2 shows the overall schematic structure of an AES-128 key schedule *KS* consisting of 11 round keys, including the secret master key in round 0 (highlighted in blue). A real AES-128 key schedule is shown in Table 3.4. To be able to reference specific parts of the key schedule, we define a set of operations and their notation:

- 1. Each round  $r \in \{0, ..., 10\}$  consists of 16 bytes, divided into four words  $w \in \{0, ..., 3\}$  of four bytes  $b \in \{0, ..., 3\}$  each.

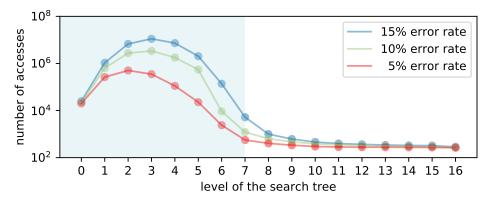

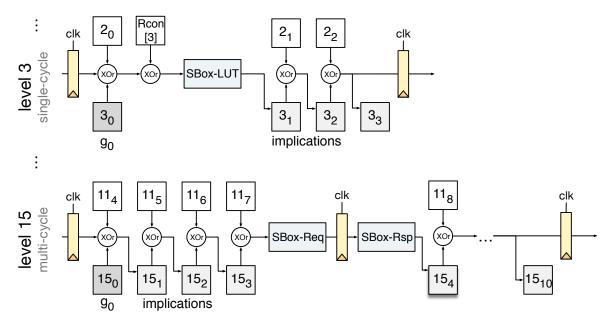

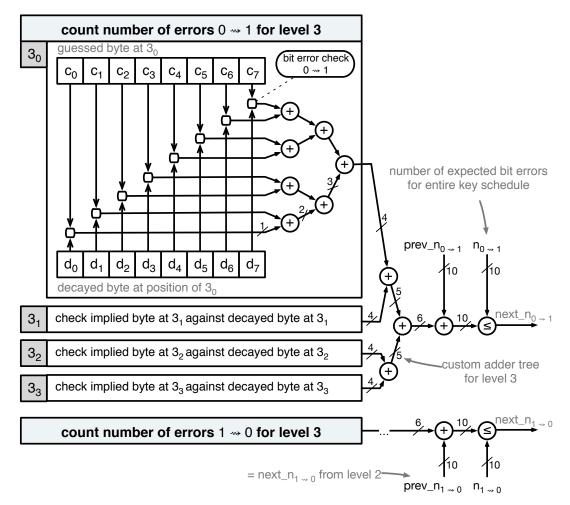

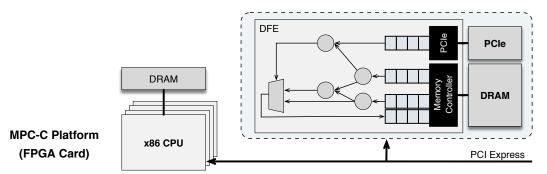

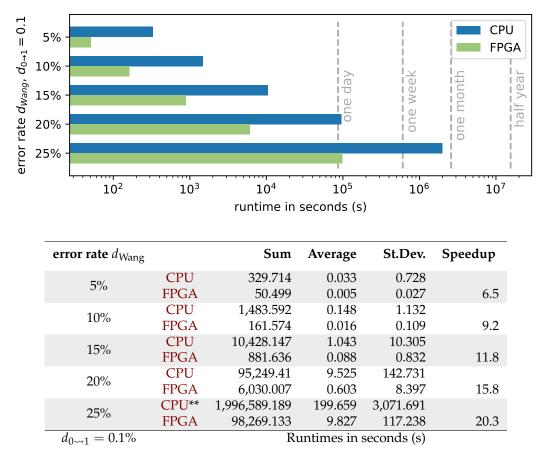

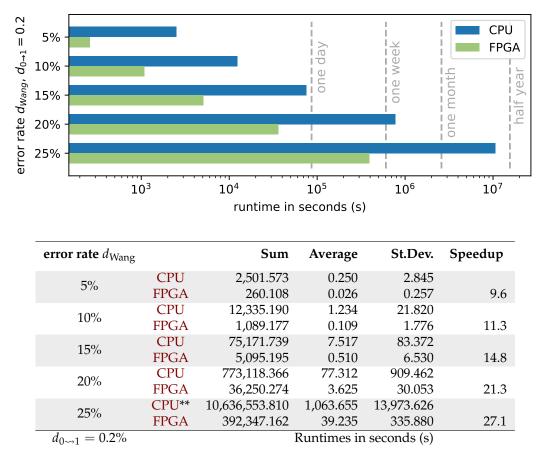

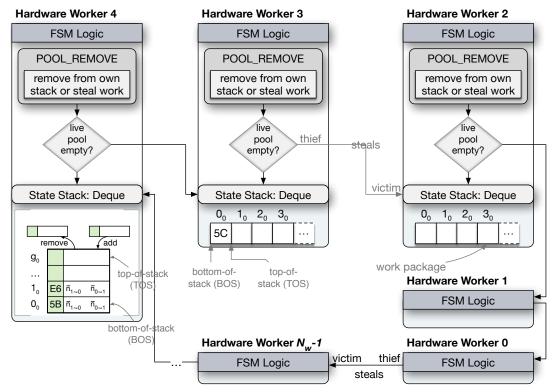

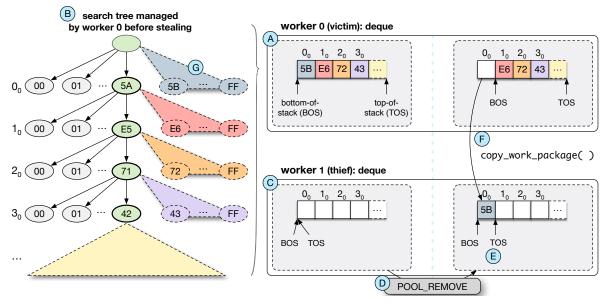

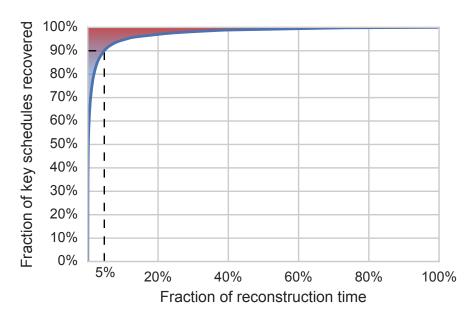

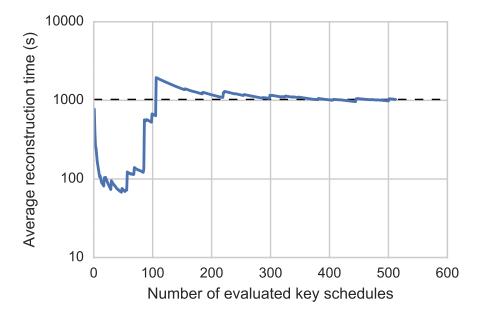

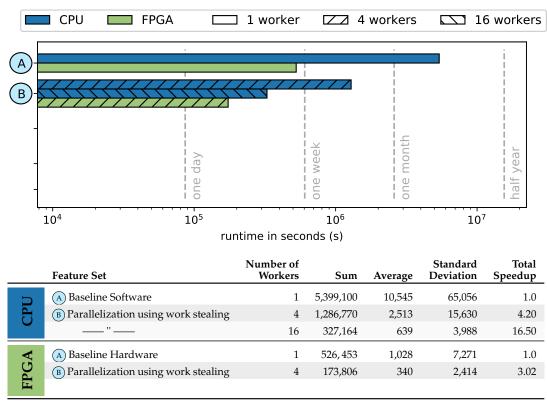

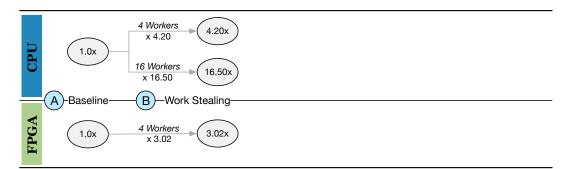

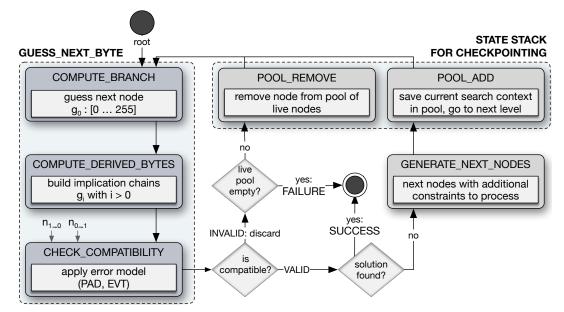

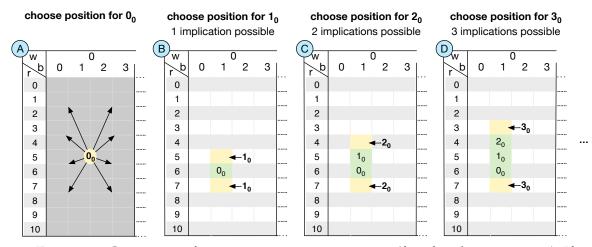

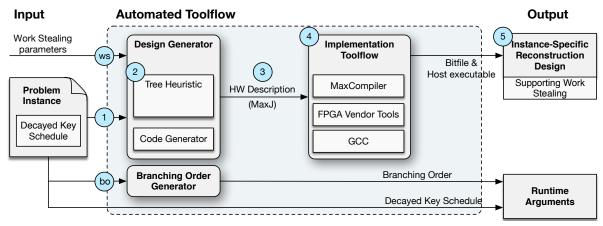

- 2. A specific byte can therefore be addressed uniquely via  $KS_{r,w,b}$ . The asterisk character \* can be used as a wildcard for certain information.